# Improving the Programmability of Heterogeneous Systems by means of Libraries

Moisés Viñas Buceta

PhD Thesis

2016

Department of Electronics and Systems University of A Coruña, Spain

# Improving the Programmability of Heterogeneous Systems by means of Libraries

Moisés Viñas Buceta РнD Thesis March 2016

PhD Advisors:

Basilio B. Fraguela Rodríguez Diego Andrade Canosa

PhD Program in Information Technology Research

Dr. Basilio Bernardo Fraguela Rodríguez

Profesor Titular de Universidad Dpto. de Electrónica y Sistemas

Universidade de A Coruña

Dr. Diego Andrade Canosa Profesor Contratado Doctor Dpto. de Electrónica y Sistemas

Universidade de A Coruña

**CERTIFICAN**

Que la memoria titulada "Improving the Programmability of Heterogeneous Systems by means of Libraries" ha sido realizada por D. Moisés Viñas Buceta bajo nuestra dirección en el Departamento de Electrónica y Sistemas de la Universidade da Coruña, y concluye la Tesis Doctoral que presenta para optar al grado de Doctor en Ingeniería Informática con la Mención de Doctor Internacional.

En A Coruña, a 11 de Marzo de 2016

Fdo.: Basilio B. Fraguela Rodríguez

Director de la Tesis Doctoral

Fdo.: Diego Andrade Canosa

Director de la Tesis Doctoral

Fdo.: Moisés Viñas Buceta Autor de la Tesis Doctoral

# Agradecimientos

En primer lugar me gustaría agradecer especialmente el arduo trabajo y la dedicación de mis directores Basilio y Diego, en cuya compañía sin duda alguna, ha sido un honor trabajar. Asimismo agradecer también a Ramón Doallo su valiosa colaboración en el desarrollo de esta Tesis y a todos los compañeros del Grupo de Arquitectura de Computadores por los grandes momentos compartidos tanto dentro del laboratorio como fuera de él.

Agradecimiento especial a mis padres, por su ejemplo y a Cris por ser mi motivación diaria.

I would like to thank the people of the 7th floor of the EWI in Delft for their kindness and friendship during my stay in The Netherlands. Specially to Ana Lucia, Henk and Jie. Again, thanks to all. I have also words of thanks to Zeki Bozkus for his collaboration and contribution to this work.

At last, I am also grateful with the following organisms for funding and supporting this work: the Computer Architecture Group, the Electronic and Systems Department and the University of A Coruña; the Galician Government under the projects Consolidation Program of Competitive Reference Groups with references 2010/06 and GRC2013/055; the Ministry of Economy and Competitiveness of Spain under the projects with references TIN2010-16735, TIN2013-42148-P; the european networks HiPEAC(FP7, refs. ICT-217068 and ICT-287759) and NESUS (COST Action, ref. IC1305) and the Spanish networks CAPAP-H.

Moisés

# Resumo

O emprego de dispositivos heteroxéneos coma co-procesadores en entornos de computación de altas prestacións (HPC) medrou ininterrompidamente nos últimos anos debido ás súas excelentes propiedades en termos de rendemento e consumo de enerxía. A maior dispoñibilidade de sistemas HPC híbridos conlevou de forma natural a necesidade de desenrolar ferramentas de programación adecuadas para eles, sendo CUDA e OpenCL as máis amplamente empregadas na actualidade. Desafortunadamente, estas ferramentas son relativamente de baixo nivel, o cal emparellado co maior número de detalles que deben de ser controlados cando se programan aceleradoras, fai da programación destes sistemas mediante elas, moito máis complexa que a programación tradicional de CPUs. Isto levou á proposta de alternativas de máis alto nivel para facilitar a programación de dispositivos heteroxéneos. Esta tesis contribúe neste campo presentando dúas librerías que melloran amplamente a programabilidade de sistemas heteroxéneos en C++, permitindo aos usuarios centrarse no que hai que facer en vez de nas tarefas de baixo nivel. As nosas propostas, a librería Heterogeneous Programming Library (HPL) e a librería Heterogeneous Hierarchically Tiled Arrays (H<sup>2</sup>TA), están deseñadas para nodos con unha ou máis aceleradoras, e para clusters heteroxéneos, respectivamente. Ambas librerías, demostraron ser capaces de incrementar a productividade dos usuarios mellorando a programabilidade dos seus códigos, e ó mesmo tempo, lograr un rendemento semellante ó de solucións de máis baixo nivel.

## Abstract

The usage of heterogeneous devices as co-processors in high performance computing (HPC) environments has steadily grown during the last years due to their excellent properties in terms of performance and energy consumption. The larger availability of hybrid HPC systems naturally led to the need to develop suitable programming tools for them, being the most widely used nowadays CUDA and OpenCL. Unfortunately, these tools are relatively low level, which coupled with the large number of details that must be managed when programming accelerators, makes the programming of these systems using them much more complex than that of traditional CPUs. This has led to the proposal of higher level alternatives that facilitate the programming of heterogeneous devices. This thesis contributes to this field presenting two libraries that largely improve the programmability of heterogeneous systems in C++, helping users to focus on what to do rather than on low level tasks. These two libraries, the Heterogeneous Programming Library (HPL) and the Heterogeneous Hierarchically Tiled Arrays (H<sup>2</sup>TA), are well suited to nodes with one or more accelerators, and to heterogeneous clusters, respectively. Both libraries have proven to be able to increase the productivity of the users improving the programmability of their codes, and at the same time, achieving performance similar to that of lower level solutions.

## Resumen

El empleo de dispositivos heterogéneos como co-procesadores en entornos de computación de altas prestaciones (HPC) ha crecido ininterrumpidamente durante los últimos años debido a sus excelentes propiedades en términos de rendimiento y consumo de energía. La mayor disponibilidad de sistemas HPC híbridos conllevó de forma natural la necesidad de desarrollar herramientas de programación adecuadas para ellos, siendo CUDA y OpenCL las más ampliamente utilizadas en la actualidad. Desafortunadamente, estas herramientas son relativamente de bajo nivel, lo cual emparejado con el mayor número de detalles que han de ser controlados cuando se programan acceleradoras, hacen de la programación de estos sistemas mediante ellas mucho más compleja que la programación tradicional de CPUs. Esto ha llevado a la propuesta de alternativas de más alto nivel para facilitar la programación de dispositivos heterogéneos. Esta tesis contribuye a este campo presentando dos librerías que mejoran ampliamente la programabilidad de sistemas heterogéneos en C++, permitiendo a los usuarios centrarse en lo que hay que hacer en vez de en las tareas de bajo nivel. Nuestras propuestas, la librería Heterogeneous Programming Library (HPL) y la librería Heterogeneous Hierarchically Tiled Arrays (H<sup>2</sup>TA), están diseñadas para nodos con una o más aceleradoras, y para clusters heterogéneos, respectivamente. Ambas librerías, han demostrado ser capaces de incrementar la productividad de los usuarios mejorando la programabilidad de sus códigos, y al mismo tiempo, lograr un rendimiento similar al de soluciones de más bajo nivel.

# Prólogo

La programación de dispositivos heterogéneos supone un desafío para los usuarios por la necesidad de enfrentarse a nuevas plataformas con nuevas herramientas y lenguajes de programación, además de exigirles especificar y gestionar muchos más aspectos. Así, entre los inconvenientes más notorios con los que ha de lidiar el programador a la hora de manejar un co-procesador, se encuentra el tedioso manejo de dos espacios de memoria separados, el del procesador y el del co-procesador. Este manejo engloba la creación de buffers en ambos espacios y el mantenimiento de la coherencia de memoria de las estructuras de datos mantenidas en ellos, lo cual implica a su vez la disposición razonada de puntos de sincronización en el programa principal para garantizar un correcto resultado. Todo este control se lleva a cabo con nuevos lenguajes de programación que exponen APIs más o menos complejas que dificultan, en algunos casos sobremanera, el desarrollo de aplicaciones con dispositivos heterogéneos. Estas APIs incluyen una cantidad notable de nuevos conceptos muchos de los cuales serán introducidos en esta tesis. Otro punto débil de la computación heterogénea es la gestion de errores pues la inmensa mayoría de los elementos de las APIs producen códigos de error destinados a facilitar la depuración de las aplicaciones heterogéneas. La gestión de estos códigos ha de ser cuidadosa pues una implementación poco rigurosa en cuanto a gestión de errores se refiere, puede suponer horas de trabajo de depuración para los programadores inexpertos.

CUDA de NVIDIA, la cual aúna plataforma y lenguaje de programación, es una de estas soluciones. Está diseñada para trabajar exclusivamente con GPUs de NVI-DIA con lo que consigue resultados de rendimiento muy buenos en dicha plataforma. Sin embargo, su dependencia del fabricante imposibilita su uso en dispositivos de otros fabricantes con lo que limita su portabilidad <sup>1</sup>. La comunidad de usuarios y fa-

<sup>&</sup>lt;sup>1</sup>Esto ha sido así históricamente, si bien recientemente ha trascendido la posibilidad de que

bricantes, se ha implicado en la eliminación de estas barreras de portabilidad dando lugar al estándar OpenCL. Debido a su carácter independiente tanto del dispositivo como del fabricante, OpenCL se ve obligado a tratar con un mayor número de conceptos y procedimientos para mantenerse genérico. Así, por ejemplo, las aplicaciones basadas en OpenCL tienen que cargar y compilar las partes de la aplicación que van a ejecutarse en los aceleradores en tiempo de ejecución, añadiendo así más complejidad al proceso.

Mención aparte requieren dispositivos heterogéneos tan populares como los de la familia Intel Xeon Phi. La programación de estos dispositivos no es patrimonio exclusivo de herramientas propias de entornos heterogéneos como el ya mencionado OpenCL, sino que puede relizarse mediante los lenguajes tradicionales de programación de CPUs. Su arquitectura many-core con procesadores x86 permite la ejecución de aplicaciones secuenciales C/C++ así como aplicaciones multiproceso con tecnologías consolidadas y propias de sistemas con memoria compartida como OpenMP o memoria distribuida como MPI. Este hecho diferenciador permite evitar el engorro de introducir al usuario en un nuevo lenguaje de programación con los inconvenientes antes citados. Sin embargo, lo que a priori puede parecer una ventaja se torna en limitación hasta cierto punto, habida cuenta de que el código desarrollado deja de ser portable a otros sistemas heterogéneos.

En los últimos años, una buena parte de la investigación en computación heterogénea se ha centrado en mejorar las interfaces disponibles para su uso de tal forma que se oculte al usuario la mayor parte de los conceptos y tareas propios de este tipo de sistemas, enmarcándose esta tesis en esta área de trabajo. En concreto, nos propusimos facilitar la programación portable de todo tipo de sistemas heterogéneos mediante sucesivas mejoras de la librería de alto nivel *Heterogeneous Programming Library* (HPL). Esta librería, basada en OpenCL, permitía al inicio de nuestro trabajo programar sistemas basados en un único dispositivo heterogéneo expresando los códigos a ejecutar en el acelerador mediante un lenguaje embebido en C++. El uso del lenguaje embebido permitía desarrollar los programas utilizando un único fichero fuente e integrar mejor el código principal del programa con el del acelerador. No obstante, HPL presentaba muchas limitaciones que no permitían el desarrollo de

otros fabricantes implementen su propio compilador de CUDA en sus arquitecturas. Tal es el caso de AMD quien ha admitido esta posibilidad abiertamente.

aplicaciones genéricas heterogéneas y que fuimos resolviendo a lo largo de esta tesis. Así, a partir de la primera versión de HPL, y siguiendo un desarrollo iterativo, se fueron incorporando nuevas funcionalidades que resumimos a continuación:

Kernel nativos: La primera versión de HPL sólo permitía la escritura de kernels usando el lenguaje embebido de HPL. Esto impedía aprovechar los kernels ya escritos usando OpenCL, a los que denominamos en esta tesis kernels nativos. En esta primera iteración, se añadió la posibilidad de usar kernels que ya estuvieran escritos en OpenCL dentro de aplicaciones HPL. Con una interfaz muy simple, HPL permite ahora el empleo de kernels nativos.

Ejecución multi-dispositivo en sistemas de memoria compartida: Tras la realización de esta Tesis, HPL facilita el uso eficiente de todos los dispositivos OpenCL conectados a un sistema. Para ello permite por un lado realizar ejecuciones paralelas no sólo en dichos dispositivos sino también en la CPU principal del sistema, y por otro tener múltiples copias de un mismo array soportado por el tipo de datos Array en HPL, en varios dispositivos incorporando un sistema de gestión de memoria que mantiene automáticamente la coherencia de dichas copias. Este mecanismo, además de proporcionar al usuario una visión secuencialmente consistente de cada Array que oculta las distintas copias que debe crear el runtime, se adapta a las propiedades de los dispositivos para reducir el tiempo de intercambio de memoria entre ellos. Por otra parte, para facilitar la división de trabajo y datos entre los dispositivos involucrados en una ejecución, HPL define el concepto de Subarray como parte constituyente de un Array. Un Subarray tiene la entidad de un Array pero mantiene la coherencia de memoria con el Array del que forma parte. A partir de esta idea se diseñaron varios sistemas de distribución de trabajo en los entornos multi-dispositivo de HPL alcanzando buenas cotas de programabilidad en estos sistemas cada vez más comunes. Una de estas propuestas incluye modelos analíticos que reparten automáticamente el trabajo entre los dispositivos de forma que se maximice el rendimiento, obteniendo resultados excelentes en nuestros experimentos.

Mantenimiento automatizado de regiones solapadas: Las computaciones en plantilla (stencil) son operaciones que suelen basarse en los elementos vecinos

de un dato dado para calcular el elemento correspondiente del array de salida. Este tipo de cálculos están muy presentes en una gran cantidad de ámbitos como resolutores de ecuaciones diferenciales, simuladores o procesadores de imágenes. Su implementación en entornos multi-dispositivo supone la existencia de regiones replicadas de los arrays utilizados en los dispositivos, para que cada uno disponga de la información necesaria para poder hacer las computaciones asociadas a los elementos ubicados en los bordes de la región que les ha sido asignada. HPL incorpora una nueva funcionalidad para el mantenimiento automático de la coherencia de estas regiones replicadas, facilitando así la implementación de este tipo de problemas.

Ejecución multi-dispositivo en sistemas de memoria distribuida : El siguiente paso lógico era facilitar la programación de clústers heterogéneos. Así, HPL ha sido integrada en una librería que mejora la programabilidad de aplicaciones en sistemas de memoria distribuida, Hierarchically Tiled Arrays (HTA), dando como resultado la librería Heterogeneous Hierarchically Tiled Arrays (H<sup>2</sup>TA). La posibilidad de explotar la localidad así como de expresar paralelismo con mucho menos esfuerzo que soluciones de más bajo nivel, hacen de HTA una base adecuada sobre la que desarrollar una solución propia para este tipo de sistemas. Así, H<sup>2</sup>TA permite la ejecución de aplicaciones HPL en un clúster con uno o varios dispositivos OpenCL por nodo. Manteniendo una API muy similar a HPL, H<sup>2</sup>TA produce aplicaciones multiproceso con un esfuerzo muy inferior y rendimiento similar al de soluciones de más bajo nivel.

De esta forma, las librerías que proponemos permiten desarrollar aplicaciones que utilizan desde un único acelerador hasta todo un cluster heterogéneo ofreciendo la máxima programabilidad para ello, y teniendo una sobrecarga mínima con respecto a implementaciones realizadas a bajo nivel. Por otra parte, están desarrolladas en C++, un lenguaje muy eficiente y ampliamente utilizado, siendo de hecho uno de los lenguajes más extendidos en entornos de computación de altas prestaciones. Además las soluciones aquí propuestas proporcionan la máxima portabilidad respecto a los dispositivos computacionales a utilizar gracias a que están basadas en OpenCL, el entorno estándar para la computación heterogénea, el cual está soportado por todos los grandes fabricantes. Ello ha permitido que en esta tesis se incluyan resultados de pruebas realizadas sobre varios tipos de dispositivos de distintos fabricantes.

A su vez, para probar las capacidades multi-dispositivo, nuestras librerías fueron evaluadas sobre varios dispositivos trabajando conjuntamente, tanto a nivel de nodo como de clúster.

## Metodología de trabajo

La metodología empleada es la conocida como Desarrollo Iterativo e Incremental, donde el trabajo de divide en diferentes fases o iteraciones y cada una de ellas finaliza con un producto perfectamente funcional con la funcionalidad de la iteración anterior y la incorporada en la iteración actual.

Esta tesis cuenta con 5 iteraciones:

#### B1.- Iteración 0 (Iteración inicial):

- 11. Análisis: Librería inicial que permita lanzar un kernel usando un lenguaje embebido.

- 12. Diseño/Codificación:

- Tipo de datos Array.

- Creación automática del código OpenCL.

- Gestión transparente de elementos de OpenCL.

- Coherencia automática de memoria.

- 13. Pruebas: Tests y "benchmarks" exhaustivos con comprobación de resultados usando kernels escritos con el lenguaje embebido.

#### B2.- Iteración 1

- 21. Análisis: Incorporación de kernels nativos.

- 22. Diseño/Codificación:

- Establecer vínculo entre HPL y OpenCL: Cabecera de kernel y método de vínculo.

- Plantillas para indicar la dirección de los argumentos del kernel nativo.

23. Pruebas: Tests y "benchmarks" con kernels nativos.

#### B3.- Iteración 2

- 31. Análisis: Extensión de la interfaz de HPL para facilitar el desarrollo de aplicaciones multi-dispositivo.

- 32. Diseño/Codificación:

- Distintos métodos de reparto de trabajo: Arrays separados, basado en Subarrays; esto es, subregiones de Arrays, y basado en anotaciones.

- Nuevo objeto de selección de regiones en arrays para su distribución posterior.

- Selección de conjuntos de trabajo y dispositivos.

- Autobalanceador de carga de trabajo entre un conjunto de dispositivos.

- 33. Pruebas: Tests y "benchmarks" para la ejecución multi-dispositivo y comparación con versiones implementadas con OpenCL nativo.

#### B4.- Iteración 3

- 41. Análisis: Extensión de la interfaz de HPL para el tratamiento de aplicaciones multi-dispositivo con regiones solapadas debido a computaciones en plantilla (stencils).

- 42. Diseño/Codificación:

- Modificación interfaz multi-dispositivo basado en anotaciones.

- Incorporación de método de sincronización automática de regiones fantasma, esto es, fragmentos de arrays replicados en varios dispositivos pero donde sólo uno tiene la responsabilidad de su actualización

- 43. Pruebas: Tests y "benchmarks" con computaciones con plantillas.

#### B5.- Iteración 4

- 51. Análisis: Uso de HPL en sistemas de memoria distribuida tales como clusters  $(H^2TA)$ .

- 52. Diseño/Codificación:

- Estudio de la librería HTA (Hierarchically Tiled Arrays library) para la mejora del desarrollo de aplicaciones multi-proceso.

- Integración de HPL en HTA:

- Nueva interfaz de usuario: Semejante a la de HPL para reducir la curva de aprendizaje.

- Mecanismo de sincronización de memoria entre las estructuras de datos de HTA y HPL.

- 53. Pruebas: "Benchmarks" en H<sup>2</sup>TA para probar su funcionamiento y en MPI+OpenCL para las comparaciones pertinentes.

#### Medios

Para la elaboración de la tesis se emplearon los medios detallados a continuación:

- Soporte económico proporcionados por el Grupo de Arquitectura de Computadores de la Universidade da Coruña y la propia Universidade da Coruña (bolsa predoutoral UDC Conv. 2013)

- Redes de investigación bajo las que se llevó a cabo esta tesis:

- Red Gallega de Computación de Altas Prestaciones II.

- High-Performance Embedded Architectures and Compilers Network of Excellence, HiPEAC2 NoE (ref. ICT-217068).

- High-Performance Embedded Architectures and Compilers Network of Excellence, HiPEAC3 NoE (ref. ICT-287759).

- Network for Sustainable Ultrascale Computing (NESUS). ICT COST Action IC1305.

- Open European Network for High Performance Computing on Complex Environments (ComplexHPC). ICT COST Action IC0805

- Red de Computación de Altas Prestaciones sobre Arquitecturas Paralelas Heterogéneas (CAPAP-H2) (ref. TIN 2009-08058-E).

- Red de Computación de Altas Prestaciones sobre Arquitecturas Paralelas Heterogéneas (CAPAP-H3) (ref. TIN 2010-12011-E).

- Red de Computación de Altas Prestaciones sobre Arquitecturas Paralelas Heterogéneas (CAPAP-H4) (ref. TIN 2011-15734-E).

- Red de Computación de Altas Prestaciones sobre Arquitecturas Paralelas Heterogéneas (CAPAP-H5) (ref. TIN 2014-53522-REDT).

- Red de Tecnologías Cloud y Big Data para HPC (Xunta de Galicia, ref. 2014/041)

- Consolidación y Estructuración de Unidades de Investigación Competitivas: Centro de Investigación en Tecnoloxías da Información e as Comunicacións (CITIC) (ref. CN 2010/211))

- Proyectos de investigación que financiaron esta tesis:

- Architectures, Systems and Tools for High Performance Computing (Ministerio de Economía y Competitividad, TIN2010-16735).

- Consolidación y Estructuración de Unidades de Investigación Competitivas: Grupo de Arquitectura de Computadores de la Universidad de A Coruña (Xunta de Galicia, ref. 2010/6)

- Consolidación y Estructuración de Unidades de Investigación Competitivas: Grupo de Arquitectura de Computadores de la Universidad de A Coruña (Xunta de Galicia, GRC2013-055).

- Nuevos desafíos en la computación de altas prestaciones: Desde arquitecturas hasta aplicaciones. (Ministerio de Economía y Competitividad, TIN2013-42148-P).

- Clúster pluton del Grupo de Arquitectura de Computadores de la Universidade da Coruña.

- 8 Nodos con CPU 2xIntel Xeon E5-2660 de 8 cores y 64 GB de RAM. Cada nodo cuenta con una GPU NVIDIA K20m con 5 GB de RAM. La red de interconexión es Infiniband FDR.

- 4 Nodos con CPU Intel Xeon X5650 de 6 cores y 12 GB de RAM. Cada nodo cuenta con dos GPUs NVIDIA M2050 con 3 GB de RAM cada una. La red de interconexión es Infiniband QDR.

- 1 Nodo con CPU 2xIntel Xeon E5-2660 de 8 cores y 64 GB de RAM. Cuenta con un accelerador Intel Xeon Phi 5110 de 60 cores y 8 GB de RAM.

- Máquina Mercurio del Grupo de Arquitectura de Computadores de la Universidade da Coruña. 1 Nodo con CPU Intel Core 2 con 2 GB de RAM. Cuenta con una GPU AMD HD6970 con 2GB de RAM.

- Máquina Fermi del Departamento de Computación da Kadir Has Üniversitesi.

1 Nodo con CPU 4xIntel Xeon E5506 de 2 cores y 24 GB de RAM. Cuenta con una GPU NVIDIA C2050 con 3GB de RAM.

- Estancia de 3 meses en el grupo PDS del Prof. Henk Sips en la Delft University of Technology.

#### Conclusiones

Durante años, la computación de altas prestaciones, HPC por sus siglas en inglés, ha estado en manos de las CPUs tradicionales. Los clústers, entendidos históricamente como agregaciones de computadores con una o varias CPUs, han permitido la ejecución de aplicaciones paralelas por medio de entornos tan maduros actualmente como OpenMP o MPI, orientados a sistemas de memoria compartida y distribuida, respectivamente. La introducción de dispositivos heterogéneos como FPGAs, GPUs o procesadores many-core en HPC, ha despertado el interés en crear herramientas de programación para estas plataformas. La mayoría de las alternativas para programar estos dispositivos son fuertemente dependientes del tipo de dispositivo o fabricante en cuestión. OpenCL es el primer estándar que intenta desacoplar el código desarrollado del hardware utilizado, proporcionando una portabilidad real del código entre las plataformas. Un gran número de fabricantes ha desarrollado sus propias implementaciones del estándar OpenCL para sus dispositivos. Como consecuencia los códigos OpenCL pueden ser ejecutados en un amplio rango de dispositivos heterogéneos sin necesidad de alterar el código fuente. Las principales limitaciones de OpenCL son: (1) el esfuerzo de programación necesario para desarrollar aplicaciones OpenCL es alto, sobre todo para programadores no familiarizados con la programación paralela, (2) OpenCL no propociona portabilidad automática de rendimiento, esto es, para maximizar el rendimiento hemos de optimizar manualmente un código para cada plataforma en la que es ejecutado, y (3) OpenCL no soporta la programación de sistemas distribuidos, en cuyo caso éste ha de ser combinado con soluciones para entornos distribuidos como MPI. Muchos trabajos han abordado estas limitaciones de muchas formas. Entre otros, hemos de mencionar la librería Heterogeneous Programming Library (HPL) [22], la cual está basada en OpenCL y facilita notablemente el desarrollo de aplicaciones mono-dispositivo, abordando por tanto la primera de las limitaciones mencionadas. Esta Tesis profundiza en el uso de HPL como herramienta para superar las limitaciones mencionadas de OpenCL: mejorando en lo posible la programabilidad de los kernels HPL, proporcionando una portabilidad efectiva de rendimiento y un soporte para la programación de sistemas distribuidos compuestos por nodos heterogéneos. Además, inicialmente HPL no proporcionaba mecanismos para la programación de sistemas multi-dispositivo, donde varios dispositivos en el mismo nodo puedan ser usados al mismo tiempo. Esta limitación ha sido superada en esta Tesis.

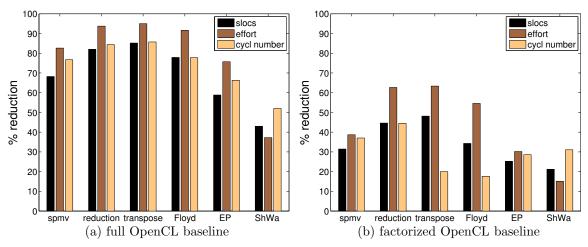

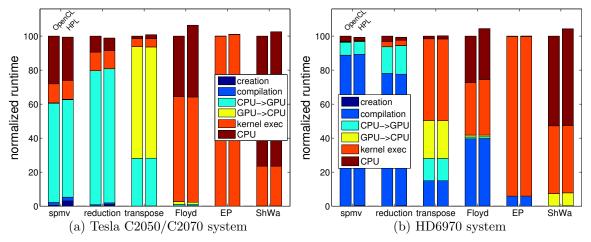

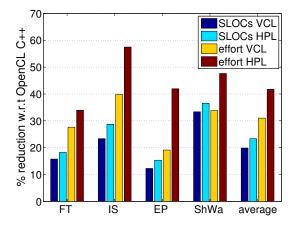

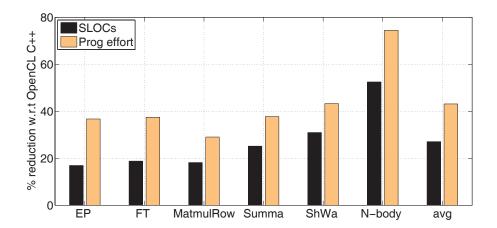

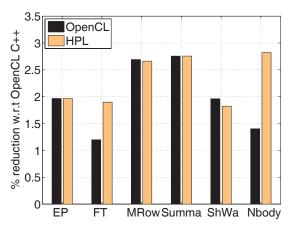

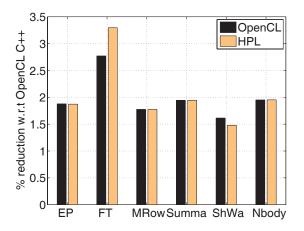

Uno de los principales inconvenientes de HPL era que los kernels habían de ser escritos en un lenguaje embebido similar a C++. El uso de kernels OpenCL nativos no estaba soportado, lo cual limitaba el uso de código legacy y el empleo de optimizaciones de OpenCL de bajo nivel o propias del fabricante. Esta limitación ha sido superada en el Capítulo 2 con la extensión de HPL para dar soporte a kernels OpenCL nativos, además de los kernels escritos con el lenguage embebido original. Este capítulo también introduce otras nuevas funcionalidades para facilitar la escritura de kernels usando el lenguaje embebido. La evaluación de estas extensiones de HPL ha arrojado datos muy satisfactorios. Durante toda la Tesis, esta evaluación ha tenido dos vertientes, la programabilidad y el rendimiento. La programabilidad se basa en las métricas: líneas de código fuente (SLOCs), esfuerzo de programación (PE) [55] y número ciclomático (CN) [77]. El rendimiento siempre se ha obtenido comparando la ejecución de la librería con nueva funcionalidad con una ejecución de referencia. Cuando los kernels se escriben usando el lenguage embebido, la reducción de SLOCs, PE y CN de todo el programa es un 34 %, 44 % y un 30 %, respectivamente con respecto a versiones de referencia escritas usando OpenCL C++. Mientras tanto, el sobrecoste medio en términos de rendimiento de HPL se sitúa por debajo del 5%. Conviene mencionar aquí que estas pruebas de rendimiento se llevaron a

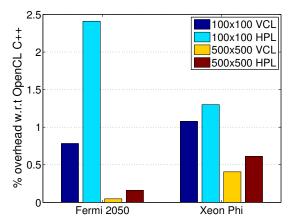

cabo sobre dispositivos de varios fabricantes. Siguiendo esta misma línea, el soporte de kernels OpenCL nativos ha cosechado también buenos resultados de rendimiento y programabilidad. De esta forma, HPL redujo las SLOCs y el PE del programa de host en un 23 % y un 42 % respectivamente, manteniendo las diferencias de rendimiento cercanas a cero. Esta mejora generalizada en las métricas también se pudo observar tras la extensa comparación realizada entre HPL y una de las aproximaciones análogas más maduras, ViennaCL [86]. Conviene recordar que todas las mejoras realizadas sobre HPL se han evaluado con benchmarks verificables incluyendo una aplicación real de simulación de fluídos [102].

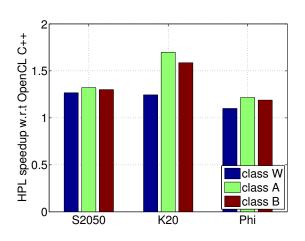

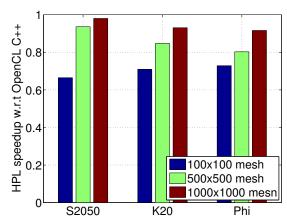

La falta de soporte para sistemas con varios dispositivos era otra importante limitación de la versión inicial de HPL. Esta limitación ha ido creciendo en importancia recientemente dado lo comunes que son nodos u ordenadores compuestos de uno o más dispositivos, y mientras que OpenCL puede ser usado para programar aplicaciones que usen varios dispositivos al mismo tiempo, esto requiere de un importante esfuerzo de programación. Con vistas a tratar esta realidad, HPL fue extendida para dar soporte a sistemas heterogéneos con varios dispositivos. Dicha extensión supuso cambios tanto a nivel interno, definiendo un nuevo mecanismo de coherencia de memoria que diese soporte a las diferentes copias de un array alojadas en los distintos dispositivos implicados, como en la API, que fue también extendida para soportar el uso de varios dispositivos al mismo tiempo en una aplicación. El nuevo mecanismo de coherencia de memoria, probado con una sencilla implementación multi-dispositivo consiguió una rebaja de SLOCs de un 27 % y de un 43 % del PE, tomando como referencia implementaciones realizadas usando OpenCL C++. El rendimiento también se vio beneficiado gracias a la naturaleza adaptativa de HPL, la cual es aportada por la selección automática del método más eficiente para el volcado de datos entre los espacios de memoria de los dispositivos. Este es un ejemplo de mecanismo de portabilidad de rendimento introducido en HPL en esta Tesis. Este hecho se hace patente principalmente en aquellas aplicaciones con un mavor intercambio de datos entre dispositivos, alcanzando speedups medios del  $28\,\%$ y máximos del 106 % para este tipo de aplicaciones y con respecto a ejecuciones de referencia escritas en OpenCL C++.

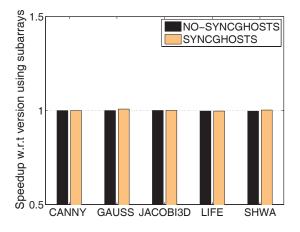

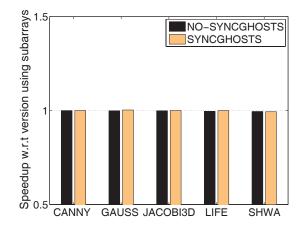

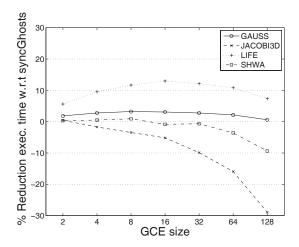

Los cambios en la interfaz son debidos principalmente a los tres mecanismos propuestos para distribuir una carga de trabajo entre varios dispositivos, desde el más manual basado en subarrays, donde el usuario ha de seleccionar explícitamente la porción de Array que ha de procesar en cada momento, hasta el más automático basado en anotaciones, donde el usuario sólo indica la dimensión por la que han de trocearse los Arrays, pasando por la versión intermedia basada en los planes de ejecución que otorga más libertad al usuario pero evitando la definición de los subarrays. Este último mecanismo incluye la posibilidad de permitir balancear automáticamente la carga de trabajo entre los dispositivos disponibles en el sistema de una forma muy sencilla. Particularmente, el usuario sólo ha de indicar los dispositivos que quiere utilizar y HPL calculará el reparto de trabajo más apropiado para ellos. Con estos tres esquemas se alcanzan reducciones máximas del PE del 76.7 % con respecto a códigos de referencia escritos en OpenCL C++. Por su parte y gracias al carácter adaptativo de HPL, la mejora de rendimiento llega a alcanzar el máximo de 146 % en comparación con los mismos códigos de referencia. Asimismo, el reparto automático de trabajo, soportado en el mecanismo basado en planes de ejecución, arroja también resultados óptimos en la mayoría de los experimentos, quedando, en el peor de los casos, un 6.3% por debajo del rendimiento de la mejor distribución de trabajo lograda mediante una búsqueda exhaustiva. La última mejora del soporte de aplicaciones multi-dispositivo en HPL propuesta en esta Tesis consistió en un mecanismo para la actualización automática de filas fantasma que aparecen habitualmente en aplicaciones con computaciones en plantilla. Esta mejora, denominada syncGhosts, fue evaluada mediante varios experimentos incluyendo aplicaciones reales. Los resultados de éstos mejoran los buenos datos obtenidos tras la aplicación de los tres mecanismos de distribución propuestos. Así, mientras que con un enfoque basado en anotaciones HPL reduce la media del PE en un  $20.5\,\%$ respecto a usar el enfoque basado en subarrays, esta reducción alcanza el 79.5 % al usar la técnica de syncGhosts conjuntamente con el esquema multi-dispositivo basado en anotaciones. En particular, para la aplicación de procesado de imágenes, CANNY, la reducción alcanza el 96.7%. Para medir con más precisión el impacto que este mecanismo pudiera tener en el tiempo de ejecución total de la aplicación, se midió su rendimiento en sistemas con dos y tres dispositivos y en ninguno de ellos las diferencias de rendimiento superan el 1%, asegurando la robustez de la implementación con esquemas de repartos de datos más complejos.

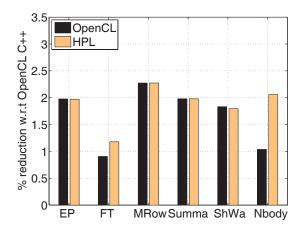

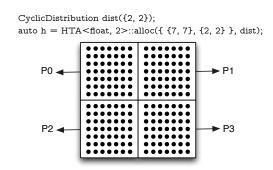

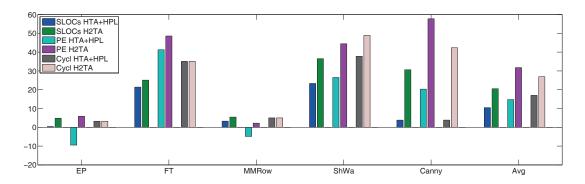

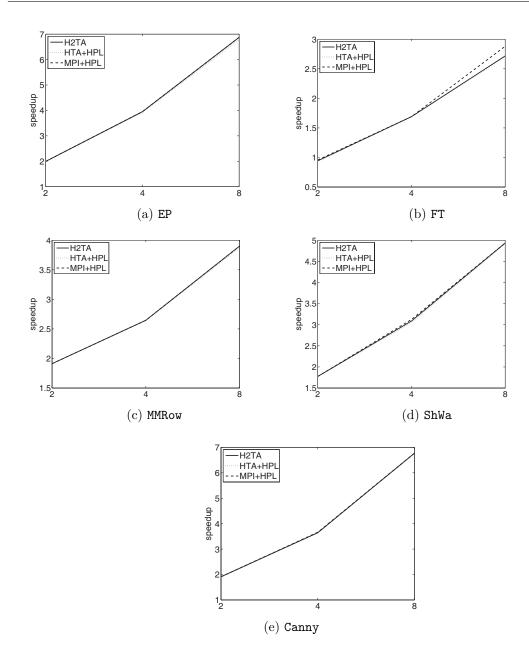

La última cuestión abordada en esta Tesis es la programación de sistemas distribuidos compuestos de nodos con dispositivos heterogéneos. Ésto se logró a través

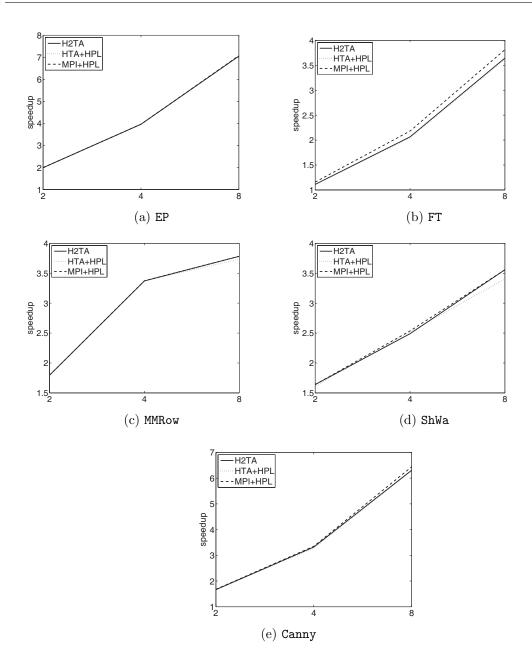

de la integración de la librería Hierarchically Tiled Array (HTA) [6] y HPL dando lugar a la librería Heterogeneous Hierarchically Tiled Arrays (H<sup>2</sup>TA). Esta librería está basada en el tipo de datos abstracto HTA, que representa a un array dividido jerárquicamente en bloques o submatrices. Estos bloques pueden estar distribuidos en un clúster y ser procesados en paralelo, proporcionando al usuario una visión global de los datos distribuidos. La librería H<sup>2</sup>TA propuesta permite el uso por parte de los programadores de los dispositivos con soporte OpenCL disponibles en un cluster, aprovechándose de las propiedades combinadas de las HTAs y de la sencillas semántica y API de HPL. Los resultados obtenidos son muy positivos. Por ejemplo, si comparamos la programabilidad de las H<sup>2</sup>TAs con la de una aproximación formada por la combinación de HPL y la librería MPI para las comunicaciones, la cual ya disfruta de una mejora significativa de programabilidad respecto a soluciones de más bajo nivel, H<sup>2</sup>TAs reducen las SLOCs, el PE y en CN en un 20.5 %, 31.8 % y un 26.9 %, respectivamente. Estos resultados también son mejores que los obtenidos usando ambas librerías de forma separada, tal y como se demuestra en el Capítulo 4 comparando aplicaciones basadas en H<sup>2</sup>TA con versiones escritas combinando HTAs y HPL. En cuanto al rendimiento, H<sup>2</sup>TA mantiene una pérdida de rendimiento media con respecto a soluciones basadas en MPI por debajo del 1%, lo cual, y teniendo en cuenta los resultados de programabilidad, no hace sino justificar este desarrollo.

### Principales contribuciones

- Estudio y análisis de múltiples soluciones para computación heterogénea.

- Estudio y prueba de diferentes arquitecturas y entornos.

- Implementación de soluciones híbridas resultantes de la fusión de varios paradigmas.

- Diseño, implementación y prueba de una solución para el problema de computación heterogénea:

- un proceso con uno o varios dispositivos en un nodo,

- varios procesos con uno o varios dispositivos por nodo en un clúster heterogéneo.

■ Estudio exhaustivo de programabilidad y rendimiento de esta solución comparándolos con los de otras alternativas notorias existentes.

## Publications from the thesis

- Viñas, M.; Lobeiras, J.; Fraguela, B.B.; Arenaz, M., Amor, M. Doallo, R. Simulation of Pollutant Transport in Shallow Water on a CUDA Architecture, Proceedings of the 2011 International Conference on High Performance Computing and Simulation (HPCS 2011), pp. 664-670, 2011.

- Viñas, M.; Lobeiras, J.; Fraguela, B.B.; Arenaz, M.; Amor, M.; García, J.A.; Castro M.J.; Doallo, R. A Multi-GPU shallow water simulation with transport of contaminants. Concurrency and Computation, 25(8), pp. 1153-1169, 2013.

- Lobeiras, J.; Viñas, M.; Amor, M.; Fraguela, B.B.; Arenaz, M.; García, J.A.; Castro, M.J. Parallelization of Shallow Water Simulations on Current Multithreaded Systems. International Journal of High Performance Computing Applications, 27(4), pp. 493-512, 2013.

- Viñas, M.; Bozkus, Z.; Fraguela B.B. Exploiting Heterogeneous Parallelism with the Heterogeneous Programming Library. Journal of Parallel and Distributed Computing, 73(12), pp. 1626-1638, 2013.

- Viñas, M.; Bozkus, Z.; Fraguela B.B. Heterogeneous Programming Library: A Framework for Quick Development of Heterogeneous Applications, Proceedings of the ACACES 2013, pp. 69-72, 2013.

- Viñas, M.; Bozkus, Z.; Fraguela B.B. Heterogeneous Programming Library: A Framework for Facilitating the Exploitation of Heterogeneous Applications, Proceedings of the 17th Workshop on Compilers for Parallel Computing, (CPC'13), 2013.

- Viñas, M.; Bozkus, Z.; Fraguela B.B.; Andrade, D.; Doallo, R. Exploiting multi-GPU systems using the Heterogeneous Programming Library, Proceedings of the 14th Conference on Computational and Mathematical Methods in Science and Engineering (CMMSE 2014), 2014.

- Viñas, M.; Fraguela B.B.; Bozkus, Z.; Andrade, D. Improving OpenCL Programmability with the Heterogeneous Programming Library, Proceedings of the International Conference on Computational Science (ICCS 2015), 2015.

- Viñas, M.; Bozkus, Z.; Fraguela B.B.; Andrade, D.; Doallo, R. Developing adaptive multi-device applications with the Heterogeneous Programming Library. The Journal of Supercomputing, 71(6), pp. 2204-2220, 2015.

# Contents

| 1. | Intr | oduction                                                      | 1         |  |  |  |

|----|------|---------------------------------------------------------------|-----------|--|--|--|

|    | 1.1. | Heterogeneous Computing                                       |           |  |  |  |

|    | 1.2. | OpenCL                                                        | 4         |  |  |  |

|    |      | 1.2.1. The Platform Model                                     | 5         |  |  |  |

|    |      | 1.2.2. The Execution Model                                    | 6         |  |  |  |

|    |      | 1.2.3. Memory Model                                           | 8         |  |  |  |

|    |      | 1.2.4. Example: vectorAddition                                | 10        |  |  |  |

|    |      | 1.2.5. OpenCL C++ bindings                                    | 14        |  |  |  |

|    | 1.3. | High Level Proposals in Single Device Environments            | 16        |  |  |  |

|    |      | 1.3.1. Support for common and skeletal operations             | 16        |  |  |  |

|    |      | 1.3.2. Compiler directives                                    | 16        |  |  |  |

|    |      | 1.3.3. Libraries that improve the usability of low level APIs | 17        |  |  |  |

|    | 1.4. | High level proposals that target multi-device systems         | 18        |  |  |  |

|    | 1.5. | Heterogeneous Clusters                                        | 19        |  |  |  |

|    | 1.6. | Thesis approach and contributions                             | 20        |  |  |  |

|    |      |                                                               |           |  |  |  |

| 2. | The  | Heterogeneous Programming Library                             | <b>25</b> |  |  |  |

XXX CONTENTS

|    | 2.1. | Progra  | amming model                                       | 26 |

|----|------|---------|----------------------------------------------------|----|

|    | 2.2. | Librar  | y frontend                                         | 28 |

|    |      | 2.2.1.  | The Array data type                                | 29 |

|    |      | 2.2.2.  | HPL embedded language                              | 32 |

|    |      | 2.2.3.  | Host Interface                                     | 38 |

|    | 2.3. | Evalua  | ation                                              | 44 |

|    |      | 2.3.1.  | Embedded language kernels                          | 45 |

|    |      | 2.3.2.  | Native OpenCL C kernels                            | 53 |

|    | 2.4. | Relate  | ed work                                            | 56 |

|    | 2.5. | Conclu  | usions                                             | 59 |

| 3. | Mul  | lti-dev | ice computing                                      | 61 |

|    | 3.1. | Multi-  | device support in HPL                              | 62 |

|    |      | 3.1.1.  | Implementation details                             | 67 |

|    | 3.2. | Impro   | ving multi-device support                          | 70 |

|    |      | 3.2.1.  | Subarrays                                          | 70 |

|    |      | 3.2.2.  | Subkernels based on annotations                    | 72 |

|    |      | 3.2.3.  | Subkernels based on execution plans                | 73 |

|    |      | 3.2.4.  | Unified memory exploitation                        | 77 |

|    | 3.3. | Impro   | ving stencil applications                          | 78 |

|    |      | 3.3.1.  | Automatic update of the shadow regions: syncGhosts | 82 |

|    | 3.4. | Evalua  | ation                                              | 84 |

|    |      | 3.4.1.  | Naïve multi-device support                         | 86 |

|    |      | 3 / 2   | Improved multi-device support                      | 92 |

| CONTENTS | XXXI |

|----------|------|

|----------|------|

|                       |            | 3.4.3. Improved stencil applications                   | 97  |  |  |  |

|-----------------------|------------|--------------------------------------------------------|-----|--|--|--|

|                       | 3.5.       | Related work                                           | 104 |  |  |  |

|                       | 3.6.       | Conclusions                                            | 107 |  |  |  |

| 4.                    | Het        | erogeneous clusters support                            | 111 |  |  |  |

|                       | 4.1.       | Hierarchically Tiled Arrays                            | 112 |  |  |  |

|                       | 4.2.       | Heterogeneous Hierarchically Tiled Arrays              | 115 |  |  |  |

|                       |            | 4.2.1. Separate use of HTA and HPL                     | 116 |  |  |  |

|                       |            | 4.2.2. Heterogeneous cluster programming with $H^2TAs$ | 119 |  |  |  |

|                       | 4.3.       | Evaluation                                             | 122 |  |  |  |

|                       |            | 4.3.1. Programmability                                 | 124 |  |  |  |

|                       |            | 4.3.2. Performance                                     | 125 |  |  |  |

|                       | 4.4.       | Related work                                           | 127 |  |  |  |

|                       | 4.5.       | Conclusions                                            | 130 |  |  |  |

| <b>5.</b>             | Con        | Conclusions                                            |     |  |  |  |

|                       | 5.1.       | Future Work                                            | 137 |  |  |  |

| References            |            |                                                        |     |  |  |  |

| A                     | Appendices |                                                        |     |  |  |  |

| A. OpenCL Programming |            |                                                        |     |  |  |  |

# List of Figures

| 1.1.  | Platform Model                                                       | -  |

|-------|----------------------------------------------------------------------|----|

| 1.2.  | Global local index spaces                                            | 7  |

| 1.3.  | OpenCL Memory Model                                                  | Ć  |

| 1.4.  | Example of an 1-D problem in OpenCL C                                | 13 |

| 1.5.  | Example of an 1-D problem in OpenCL C++                              | 15 |

| 2.1.  | Heterogeneous Programming Library hardware model                     | 26 |

| 2.2.  | HPL running example                                                  | 29 |

| 2.3.  | Declaring a struct type to HPL in order to use it in Arrays          | 30 |

| 2.4.  | Usage of Arrays in host code                                         | 31 |

| 2.5.  | SAXPY kernel in HPL                                                  | 32 |

| 2.6.  | Generic HPL kernel to add bidimensional arrays of any type           | 33 |

| 2.7.  | Dot product kernels in HPL                                           | 34 |

| 2.8.  | Using regular C++ in a kernel to generate an unrolled matrix product | 36 |

| 2.9.  | Array creation and SAXPY kernel usage                                | 39 |

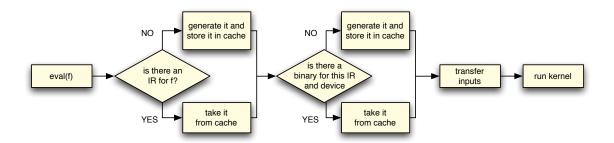

| 2.10. | Kernel invocation algorithm                                          | 41 |

| 2.11. | Saxpy using native OpenCL C kernel with HPL                          | 44 |

| 2.12. Productivity metrics reduction in HPL with respect to two OpenCL baseline implementations                      | 48 |

|----------------------------------------------------------------------------------------------------------------------|----|

| 2.13. Performance of the OpenCL and the HPL versions of the codes, normalized to the runtime of the OpenCL version   | 50 |

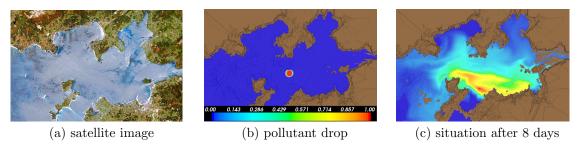

| 2.14. Simulation of evolution of a pollutant in Ría de Arousa                                                        | 51 |

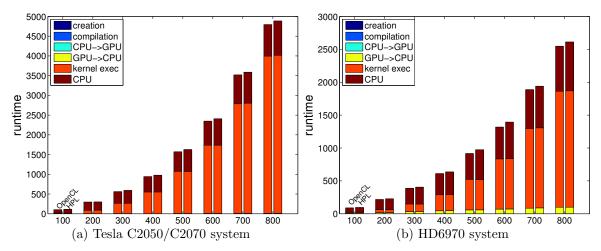

| 2.15. Runtime of the OpenCL and the HPL versions of the shallow water simulator for different problem sizes          | 53 |

| 2.16. Productivity improvement in ViennaCL and HPL with respect to the baseline                                      | 55 |

| 2.17. Overhead of ViennaCL and HPL in ShWa with respect to the baseline                                              | 55 |

| 3.1. Matrix product on a single device using HPL                                                                     | 65 |

| 3.2. Matrix product on multiple GPUs using HPL                                                                       | 65 |

| 3.3. Data exchange to implement a pipeline between devices                                                           | 67 |

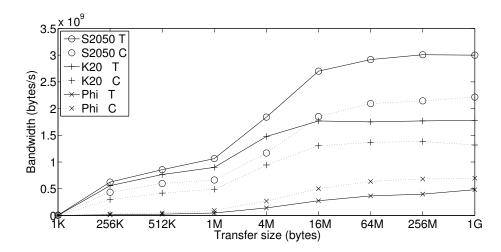

| 3.4. Bandwidth of copies between devices. T stands for two transfers in sequence and C for clEnqueueCopyBuffer usage | 69 |

| 3.5. Matrix product on multiple GPUs using subarrays                                                                 | 71 |

| 3.6. Matrix product on multiple GPUs using an execution plan                                                         | 75 |

| 3.7. SINGLE_STEP_MODEL load balancing algorithm                                                                      | 76 |

| 3.8. ITERATIVE_MODEL adaptive load balancing algorithm                                                               | 78 |

| 3.9. HPL stencil example in single-device                                                                            | 80 |

| 3.10. HPL stencil example in multi-device using subarrays                                                            | 81 |

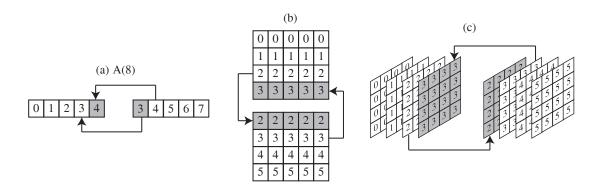

| 3.11. Examples of ghost regions for (a) 1-D, (b) 2-D and (c) 3-D problems in a problem divided by two devices        | 83 |

| 3.12. 1-D syncGhosts algorithm                                                                                       | 83 |

| 3.13. Example on multiple GPUs using subarrays with syncGhosts                                                       | 85 |

| 3.14. Example on multiple GPUs using annotations with syncGhosts 85                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.15. Reduction in the number of SLOCs and programming effort of the host side of the application when using HPL with respect to the                  |

| OpenCL C++ baseline                                                                                                                                   |

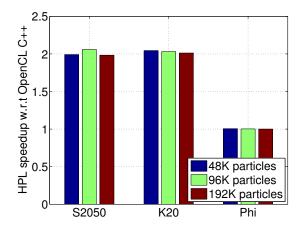

| 3.16. Speedups with S2050                                                                                                                             |

| 3.17. Speedups with K20                                                                                                                               |

| 3.18. Speedups with Xeon Phi                                                                                                                          |

| 3.19. Speedup of HPL over OpenCL for different problem sizes of FT 91                                                                                 |

| 3.20. Speedup of HPL over OpenCL for different problem sizes of ShWa 91                                                                               |

| 3.21. Speedup of HPL over OpenCL for different problem sizes of N-Body . $91$                                                                         |

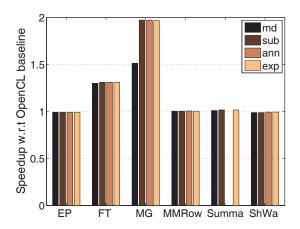

| 3.22. Performance in the S2050 system using both GPUs 95                                                                                              |

| 3.23. Performance in the K20 system using two GPUs 95                                                                                                 |

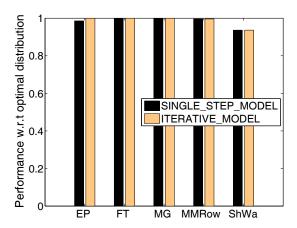

| 3.24. Relative performance of the distributions found by the analytical models with respect to the best one found when using one CPU and two K20 GPUs |

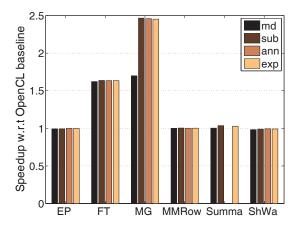

| 3.25. Performance in the S2050 system using both GPUs 101                                                                                             |

| 3.26. Performance in the K20 system using two GPUs                                                                                                    |

| 3.27. Performance improvement using 3 devices                                                                                                         |

| 3.28. Performance of <i>syncGhosts</i> versions varying the ghost region sizes and using two GPUs in K20 system                                       |

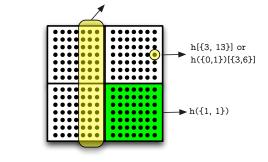

| 4.1. HTA creation                                                                                                                                     |

| 4.2. HTA indexing                                                                                                                                     |

| 4.3. HTA complex assignment example                                                                                                                   |

| 4.4. Parallel application of a user-defined function to the tiles of HTAs 115                                                                         |

| 4.5. Joint usage of HTAs and HPL                                                                                                                      |

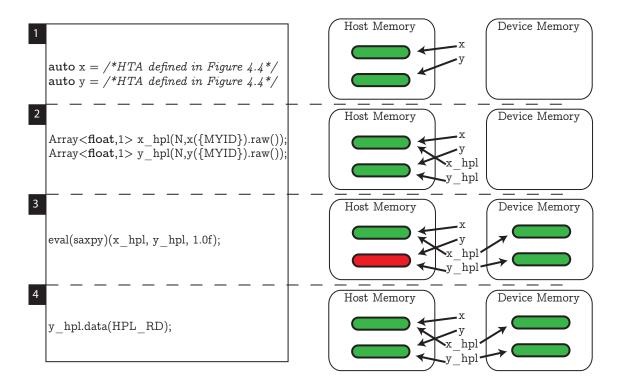

| 4.6.  | Example of the memory coherency mechanism implemented when                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | HTA and HPL are separately used                                                                                           |

| 4.7.  | $H^2TA$ example code                                                                                                      |

| 4.8.  | HPL example code                                                                                                          |

| 4.9.  | Reduction of programming complexity metrics of HTA+HPL and H²TA programs with respect to versions based on MPI+HPL 125 $$ |

| 4.10. | Speedup of the executions in Fermi using multiple devices with respect to an execution using a single device              |

| 4.11. | Speedup of the executions in K20 using multiple devices with respect to an execution using a single device                |

# List of Tables

| 1.1. | Summary of the high level proposals                                                                                                                              | 21  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1. | Predefined HPL variables                                                                                                                                         | 32  |

| 2.2. | OpenCL generating process                                                                                                                                        | 39  |

| 2.3. | Benchmarks characteristics                                                                                                                                       | 45  |

| 2.4. | NAS Parallel Benchmark EP runtimes for class C (in seconds)                                                                                                      | 52  |

| 2.5. | Benchmarks characteristics                                                                                                                                       | 54  |

| 3.1. | Benchmarks characteristics                                                                                                                                       | 87  |

| 3.2. | The Hardware Platform Details                                                                                                                                    | 89  |

| 3.3. | MG benchmark characteristics                                                                                                                                     | 93  |

| 3.4. | Programmability improvement for several strategies                                                                                                               | 93  |

| 3.5. | Slowdown of the worst distribution with respect to the best one in the two configurations tested                                                                 | 98  |

| 3.6. | Benchmark details                                                                                                                                                | 99  |

| 3.7. | Programmability improvement without and with the syncGhosts mechanism of HPL programs based on annotations with respect to versions based on explicit subarrays. | 100 |

| 4.1. | Benchmarks characteristics                                                                                                                                       | 124 |

| XXXVIII |                      | LIST | OF | TABLES |

|---------|----------------------|------|----|--------|

| 1.      | OpenCL device types. | <br> |    | 154    |

| 2.      | OpenCL device types. | <br> |    | 161    |

# Chapter 1

# Introduction

Heterogeneous: composed of diverse elements or constituents; consisting of parts of different kinds; not homogeneous. (Oxford dict.)

The relevance of the usage of computing devices with very different characteristics that cooperate in a computation has increased exponentially in the past few years. The reason for this has been the appearance of accelerators that can be programmed to perform general-purpose computations achieving larger speedups and/or power savings than traditional single-core and even multi-core CPUs.

Unfortunately this hardware heterogeneity is also reflected in the software required to program these systems since, unlike with regular CPUs, with these types of accelerators programmers are typically exposed to a number of characteristics and limitations that must be handled. This way, heterogeneous systems require much more effort to be programmed than the traditional computers because of the appearance of new concepts and tools with different restrictions. Additionally, many of the approaches to exploit heterogeneous systems are specific to one vendor or device, resulting in little portability or rapid obsolescence for the applications built on them. Open standards for programming heterogeneous systems such as OpenCL contribute to improve this situation, but the requirement of portability has led to a programming interface more complex than that of other approaches.

The purpose of this PhD Thesis is to propose tools that facilitate the programming of heterogeneous computing systems while providing the maximum portability and performance. This first chapter introduces the reader to heterogeneous computing by means of a short description of its history and current state of the subject matter. This is followed by an introduction to the only portable alternative nowadays, the OpenCL standard, which is the backend used by the tools developed in this Thesis. Next, the family of solutions for the improvement of the programmability of heterogeneous systems considering a single device, multiple devices in the same node, and heterogeneous clusters is briefly reviewed in Sections 1.3, 1.4, and 1.5, respectively. The chapter finishes with the motivation and the scope of this PhD Thesis and its contributions.

# 1.1. Heterogeneous Computing

Heterogeneous computing arises when different types of devices with compute capability are used by an application. These devices usually include one or more general purpose CPUs that collaborate with a number of so-called accelerators, which are computing systems that cannot operate on their own and to which the CPUs can offload computations. These devices, characterized by their high performance, first appeared in the market as specialized hardware that sought to satisfy the strong demand for high resolution 3D graphics in real-time. In those days, the users were able to implement their own applications for graphics visualization. At the beginning these rendering processes had to be done on the CPU using the graphics hardware only in order to display the pixels in the screen. Unfortunately, the CPU was too slow to produce attractive 3D effects. To solve this problem, the graphics hardware evolved, gradually gaining computing power, and as a result the CPU was increasingly freed from the graphics tasks. Therefore, at some point 3D applications no longer implemented their own 3D rendering algorithms on the CPU; but rather they began to rely on either OpenGL [105] or Direct3D [21], the two new standard 3D programming interfaces to communicate rendering commands the new generation of devices, called GPUs (Graphics Processing Units). GPUs are very well suited for these tasks because they offer several pipelines to execute different "shaders" or programs to compute operations on the visualization matrix. Languages, like OpenGL Shading Language [85] or High Level Shader Language [91] were the most widely used for OpenGL and Direct3D environments respectively.

Cg [76] is a proprietary language of Nvidia that allows the creation of shaders for both OpenGL and Direct3D.

The GPU tasks are executed on many data elements in parallel. Many algorithms outside the field of image rendering and processing can be accelerated applying data-parallel processing, also known as "stream processing". The first attempts at exploiting GPUs for general purpose computations, also called GPGPU, relied on the existing languages oriented to graphic tasks. However, the approach was cumbersome and there were many limitations. This, together with the large advantages observed when exploiting GPGPU, lead to the development of new programming languages as well as improved hardware for the GPUs that made them more amenable for GPGPU. This way, version 11.0 of Direct3D was equipped with a new graphic pipeline to perform tasks not related with graphics, such as stream processing, giving birth to the compute shaders, also called kernels. These are computing unities not linked to a graphical task, having on the contrary hardware suitable for general purpose computations. As a result, they demand the management of new concepts and procedures not related with graphics. Programming frameworks such as CUDA [80], Close To Metal [10], BrookGPU [25] or Brook+ [8] are the answer of manufacturers and organizations to this demand. The current situation is that, despite being supported by a single vendor, the NVIDIA CUDA platform accounts nowadays for most of the GPGPU market.

There are also accelerators that played a very important role in the raise of heterogeneous computing but have now disappeared. This is the case of the Cell processor [60] developed in the early 2000's. The Cell processor was jointly developed by Sony, Toshiba and IBM and while its main commercial application was the Sony's PlayStation 3 game console, it was also used in a number of computers as accelerator. It consisted in nine processors: one acting as a controller and the rest acting as mere processing units, all of them interconnected with a bus. Its programming relied on C/C++ with language extensions [59] to support vector types and functions to operate with those vectors that are executed in parallel distributing the work on the processing units. Despite its good performance for scientific computing, the large number of details that needed to be managed coupled with the low level of the tools available for the development of Cell applications strongly hampered the adoption of this platform beyond very specific niches, leading to its cancellation in 2009.

In contrast, there are other co-processors with a longer history that enjoy nowadays the support of an important community of developers and users. This is the case of the Field-Programmable Gate Arrays (FPGAs), a co-processor family with a long and successful history. The main difference between these devices and the GPUs is related with their hardware arquitecture. FPGAs are arrays of programmable logic blocks, memory cells and physical connections, which the programmer is in charge of programming at hardware level, instead of software level which is the case of GPUs. The compilers reconfigure the FPGA so that it becomes a custom processor designed for computing a specific kernel. Programming FPGAs has traditionally been difficult and requires expertise in specialized languages like VHDL [12] or Verilog [97]. Another successful case is the Intel Xeon Phi, which has became pretty popular as a co-processor, an important reason being its very good programmability. In fact, it can be programmed using the same tools as standard multicore systems, such as OpenMP, MPI, or pthreads because it is made up of a collection of x86 processors. This accelerator is based on a previously cancelled project of Intel called *Larrabee* that seeked to create a new family of GPUs based on x86 cores.

As we have seen, there are several families of accelerators, and worse, a large number of incompatible alternatives to program them, which makes applications based on them inherently non-portable. As a result of this situation, several organisms and manufacturers grouped under the Khronos Group brand, focused their efforts on developing a standard for heterogeneous computing, the Open Computing Language (OpenCL) [62]. Nowadays, OpenCL is supported by the large majority of the vendors of heterogeneous systems (IBM, AMD, Intel, NVIDIA, ...) and it already replaced several APIs now deprecated such as Close To Metal, BrookGPU or Brook+. Because of this portability we chose OpenCL as the backend for our efforts to improve the programmability of heterogeneous systems.

## 1.2. OpenCL

The Open Computing Language (OpenCL [62]) is an open API designed to allow the use of GPUs and other co-processors to work jointly with the CPU, in order to take advantage of the additional computing power. As a standard, OpenCL 1.0 was released in December 2008, by an independent standards consortium called The 1.2 OpenCL 5

Khronos Group. The standard has evolved from that initial version to the most recent one, the OpenCL 2.1 released in November 2015. This introduction only includes basic concepts of OpenCL and therefore, they have endured through the successive versions of the standard.

The two main features of OpenCL are the exploitation of all the OpenCL computing resources available in the system, such as multi-core CPUs and GPUs among others, and the total portability of the OpenCL codes among different manufacturers, unless vendor-specific extensions are used. The standard separates the software layer, which is a responsibility of the programmers, from the hardware layer, which is a responsibility of the manufacturers. All the hardware implementation details, such as drivers and runtime are transparent from the point of view of the software programmers.

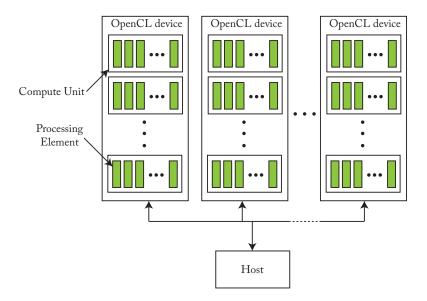

#### 1.2.1. The Platform Model

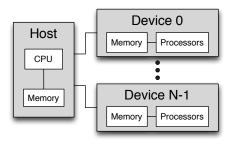

The platform model of OpenCL, illustrated in Figure 1.1, is defined as a host connected to one or more OpenCL devices. A host is any computer with a CPU. The OpenCL devices can be GPUs, FPGAs, many-core processors, ... A device consists

Figure 1.1: Platform Model

of a collection of one or more *compute units*. A compute unit is at the same time composed by one or several *processing elements*. The processing elements execute SIMD (Single Instruction, Multiple Data) instructions so that only one instruction is executed simultaneously in several processing elements.

#### 1.2.2. The Execution Model

The OpenCL execution model mainly consists of two different elements: the kernels and the host program. A kernel is the basic unit of executable code that runs on an OpenCL device. Kernels are basically C-like functions that are executed in parallel by the *processing elements* of a device. The host program is the main program, which is executed in the CPU and defines a context for the OpenCL devices and enqueues the kernel executions using command queues. The queuing is in-order but the execution of the command can be out-of-order.

#### Kernels

OpenCL defines for each kernel a N-dimensional index space of work. This workspace can have up to three dimensions. The kernel will be enqueued to be executed in the device. The OpenCL runtime creates one instance of this kernel, called work-item, per point of the defined index space. While each work-item executes the same kernel function, it does it using different data that can be identified using the global position of the work-item in the index space, which is known as global ID.

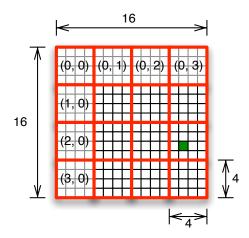

In OpenCL the work-items can be grouped in teams called work-groups. The size of each work-group is defined by its own local index space. As in the global index space, work-items can also know their position into the local index space (local ID). All the work-items that belong to a work-group share several properties. First, their execution takes place in the same compute unit because the execution of a work-group can not be split in more than one compute unit. Second, the work-items belonging to the same group share a local on-chip memory. As a result, the communication of data into a work-group can be done in a very fast way using this memory. Finally, work-items can be synchronized at a work-group level, this is, the work-group execution can be stopped at a synchronization point, concretely a

1.2 OpenCL

barrier, set by the programmer.

Figure 1.2 illustrates the example of a two-dimensional global index space of  $16 \times 16$  work-items. This index space is divided in 16 work-groups. The work-group containing the highlighted work-item has a global ID (2,3) and a local size  $4 \times 4$ . The local ID of the highlighted work-item (in green) is (2,1), although it can be also identified globally with the global ID (10,13).

#### **Host Program**

The host program is in charge of setting up and managing the execution of the kernels on the chosen OpenCL devices of the OpenCL platforms installed in the system. By means of the OpenCL API, the host can create and manipulate the following elements belonging to an OpenCL context:

- Devices: Set of OpenCL devices used by the host for kernel execution.

- Program objects, that implements a kernel or a collection of them.

- Kernels: OpenCL functions that will be executed on the device.

- Memory objects: Memory buffers used in both the host program and the OpenCL devices.

Figure 1.2: Global local index spaces

• Command queues: Objects in charge of submitting commands on the device.

When the context is created, the command queues are created and managed by the user to perform the execution of the kernels in the OpenCL devices associated to that context. Overall, the command queues accept three kind of commands:

- Kernel execution command, which runs the kernel in the device.

- Memory commands, which transfer data between the host program memory and the device memory.

- Synchronization commands, which allow the user to manipulate the order of the command execution with respect to other commands or the host program.

The user can specify two types of execution for the commands enqueued: blocking or non-blocking. If a command is blocking, the command blocks the execution of the host program until its completion. Otherwise, the host program continues its execution without waiting for the result of the command.

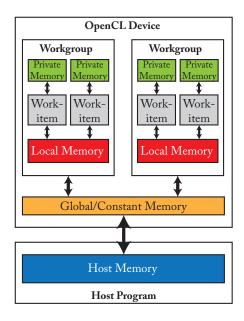

## 1.2.3. Memory Model

Figure 1.3 shows the scheme of the OpenCL memory model, which reflects four kinds of memory that a work-item can access during the execution of a kernel: Global, Local, Private and Constant memory. We describe them now in turn.

#### Global Memory

The global memory is the main and largest memory space of the device and it can span several GB. Work-items can read and write random memory positions in this memory, which is also used to communicate the host with the devices. If the kernel needs to send or receive data to/from the host application, they have to be stored in global memory. Nowadays, accelerators have several levels of cache for this memory, which help to mitigate the time penalty suffered in the global memory accesses because of the lack of locality and/or coalescence. Coalescence here refers to the ability of the hardware to combine several memory accesses into a reduced number

1.2 OpenCL

Figure 1.3: OpenCL Memory Model

of memory transactions. Briefly, a global memory access is coalesced (combined) if and only if consecutive work-items access consecutive global memory positions and this memory is aligned (i.e. its address is a multiple of the data type size). Before the introduction of global memory caches, uncoalesced accesses played a much larger role in the performance of a kernel.

#### **Local Memory**

The local memory only serves to the work-items of the same work-group, who have the same view of this memory space. It is a very fast *on-chip* memory so it can be seen as a scratchpad that can be managed by the user.

#### Private Memory

By default, all the variables defined inside a kernel are stored in this memory. Private memory has two natures. On the one hand, if a scalar variable is defined and there are registers available, that variable will be stored in a register. If an array is defined, or there are no free registers for store a scalar variable, that variable will

be stored in global memory. Register spilling is the problem that appears when the registers are overused, causing the copy of data from global memory to registers and vice-versa in order to keep in the registers the working set of the kernel. This problem can cause important performance penalties.

#### Constant Memory

The constant memory is a memory space that can be defined statically inside the kernel code, or dynamically before the kernel execution. As its name implies, it is constant for the kernels, all the changes on it being performed by the host application.

#### 1.2.4. Example: vectorAddition

This section shows an example (Figure 1.4) of a host program and its corresponding kernel. It serves as an example of the typical steps of an OpenCL application. The kernel of the example chosen uses two buffers, src and dst, and computes dst = dst + src. This code is somewhat simplified with respect to a realistic one because it does not include error checks and it assumes the existence of only one GPU. In addition, the buffers used are not initialized in order to center only on the requirements of an OpenCL application.

Firstly, Lines 6-9 define the string that contains the kernel code that will be executed on the selected device. It is a vector addition that uses two vectors src and dst defined in global memory. The memory spaces in OpenCL can be distinguished through the keywords \_\_global, \_\_local and \_\_constant. Note that it is not needed to specify a private memory space because it is the default choice inside the kernel when none is specified. The code of this kernel specifies that each work-item adds an element of the src array with an element of the same position of dst array and stores the result in the latter one. The functions get\_global\_id(int d) and get\_local\_id(int d) provide the positions in the d dimension of the calling thread in the global and local index spaces respectively.

The first step in the application is to obtain the platform found in the system (Line 14). The most relevant functions of the OpenCL API are detailed in Appendix

1.2 OpenCL 11

A. In Line 17, we obtain the identifier of the first GPU device of the chosen platform. If the system has more than one platform or device, these same calls will return pointers to the platforms and devices found.

In Line 19, a context is created for the platform and device chosen. Taking into account the context created and the device associated to it, the commandQueue object is created in Line 21.

In Line 23, the program object is created using the kernel code and it is compiled in Line 24 for the chosen device. In Line 26, the kernel object, which will be used for passing arguments and its later execution, is obtained from the program.

Lines 29-30 define the buffers that contain the data of the vectors in the device memory. Their creation includes the context they belong to and, among other parameters, the access type in the kernel. The most important types are read-only (CL\_MEM\_READ\_ONLY), write-only (CL\_MEM\_WRITE\_ONLY) and read-write (CL\_MEM\_READ\_WRITE).

In Lines 35-36 the content of the buffers is copied from the host to the device by means of the clEnqueueWriteBuffer function. In Line 35, this command is enqueued in the commandQueue passed as argument. This command performs the copy of the data pointed by src\_host in the device buffer src\_buffer. In Line 36, the same task is done for the target buffer.

Line 38-41 specify the execution parameters of the kernel. In the first place, Line 38 defines the size of the global index space of the problem. In this case it is one-dimensional with NWORKITEMS work-items. Lines 39 and 40 specify the arguments of the kernel, in this case only the buffers src\_buffer and dst\_buffer. Finally, in Line 41, the execution of the kernel kernel is launched by means of the call clenqueueNDRangeKernel specifying among others, the commandQueue that will perform the execution and the global space. It deserves to be mentioned, that in this case there is no local domain size specified (6th argument). Instead of a local domain, there is a NULL pointer so that the system is in charge of choosing the most suitable local domain for the hardware of the selected device.

Kernel invocations are not blocking. For this reason, after this point the kernel is executed in the GPU in parallel with the rest of the host code. Since the result of dst\_buffer is used in the host application after Line 43, it has to be downloaded from the GPU to the host. The transfer of the data of dst\_buffer to the host memory

pointed by dst\_host is achieved by means of the call clEnqueueReadBuffer of Line 43. Some commands like clEnqueueReadBuffer and clEnqueueWriteBuffer allow to specify their behavior in terms of synchronization by means of the BLOCKING flag (3rd argument). This is, if the BLOCKING flag is TRUE, the host application will stop until the command specified as BLOCKING has finished. Otherwise, the control will return to the host immediately after enqueueing the command. In this example, the host will be waiting for the finish of the enqueueReadBuffer command.

Finally, the elements of the resulting vector, recently copied from the device to the host, are printed on the standard output.

1.2 OpenCL

```

\#include < CL/cl.h>

#include <stdio.h>

#define NWORKITEMS 1024

const char *kernel_code =

"_kernel void vectorAddition(_global int *src, _global int *dst) { \n

dst[get\_global\_id(0)] \ += \ src[get\_global\_id(0)]; \ \backslash n \ \backslash

9

10

11

\mathbf{int} \ \mathrm{main}(\mathbf{int} \ \mathrm{argc}, \ \mathbf{char}{**} \ \mathrm{argv})

12

13

cl_platform_id platform;

14

clGetPlatformIDs (1,\,\&platform,\,NULL);

15

16

cl_device_id device;

clGetDeviceIDs(platform, CL_DEVICE_TYPE_GPU, 1, &device, NULL);

19

{\tt cl\_context\ context} = {\tt clCreateContext}({\tt NULL},\,1,\,\&{\tt device},\,0,\,{\tt NULL});

20

21

{\it cl\_command\_queue \; queue = clCreateCommandQueue(context, \; device, \; 0, \; NULL);}

22

cl_program program = clCreateProgramWithSource(context, 1, &kernel_code, NULL, NULL);

24

clBuildProgram(program, 1, &device, NULL, NULL, NULL);

25

26

{\it cl\_kernel \; kernel = clCreateKernel(program, "vectorAddition", \; NULL);}

27

int size = NWORKITEMS * sizeof(int);

28

{\it cl\_mem\ src\_buffer} = {\it clCreateBuffer} (context,\ CL\_MEM\_READ\_ONLY,\ size,\ NULL,\ NULL);

30

{\tt cl\_mem\ dst\_buffer} = {\tt clCreateBuffer} ({\tt context},\ {\tt CL\_MEM\_READ\_WRITE},\ {\tt size},\ {\tt NULL},\ {\tt NULL});

31

32

\mathbf{int} \ *\mathrm{src\_host} = (\mathbf{int}*)\mathrm{malloc}(\mathrm{size});

33

int *dst_host = (int*)malloc(size);

34

clEnqueueWriteBuffer(queue, src_buffer, CL_TRUE, 0, size, src_host, 0, NULL, NULL);

clEnqueueWriteBuffer(queue, dst_buffer, CL_TRUE, 0, size, dst_host, 0, NULL, NULL);

37

38

size_t global_work_size = NWORKITEMS;