# UNIVERSIDAD DE SANTIAGO DE COMPOSTELA FACULTAD DE FÍSICA DEPARTAMENTO DE ELECTRÓNICA Y COMPUTACIÓN

#### TESIS DOCTORAL

## Técnicas de compilación para la paralelización de códigos irregulares

Presentada por:

David Expósito Singh

Octubre 2003

Dr. Francisco Fernández Rivera, Profesor Titular de Arquitectura y Tecnología de Computadores de la Universidad de Santiago de ComposDra. María Martín Santamaría, Profesora Titular de Arquitectura y Tecnología de Computadores de la Universidad de A Coruña.

#### **CERTIFICAN:**

tela.

Que la memoria titulada "**Técnicas de compilación para la paralelización de códigos irregulares**", ha sido realizada por D. **David Expósito Singh** bajo nuestra dirección en el Departamento de Electrónica y Computación de la Universidad de Santiago de Compostela y concluye la Tesis que presenta para optar al grado de Doctor en Ciencias Físicas.

Santiago, 16 de Octubre de 2003

Dr. Francisco Fernández Rivera Codirector de la tesis Dra. María Martín Santamaría Codirectora de la tesis

Fdo. Dr. **Diego Cabello Ferrer**, Director del Departamento de Electrónica y Computación.

A mis padres y a mis hermanos

### Agradecimientos

Quiero dar mi más sincero agradecimiento a todas las personas que han contribuido a la realización de esta tesis tanto en el ámbito académico como en el personal.

El primer lugar quiero dar las gracias a mis codirectores, los profesores D. Francisco Fernández Rivera y Dña. María Martín Santamaría, por toda la ayuda que me han prestado. Ellos me dieron la oportunidad de iniciar mis estudios de doctorado, y me han ofrecido siempre todo su apoyo y colaboración. Quiero agradecerles muy especialmente todo el tiempo y esfuerzo que me han dedicado, así como la confianza que han depositado en mí.

También quiero expresar mis agradecimientos a todos los miembros del Departamento de Electrónica y Computación, y en particular a aquellos que pertenecen, o han pertenecido, al Grupo de Arquitectura de Computadores. Con ellos he compartido muchos momentos "mágicos" que han hecho que esta etapa de mi vida haya sido tan gratificante.

Gracias especialmente a aquellos con los que en algún momento he compartido despacho: Álvaro, Antonio, Dora, Inma, Juanjo, Marcos, Patricia, Pichel y Roberto. Todos ellos me ofrecieron su amistad, y me ayudaron en los momentos más difíciles.

A Antonio le debo mi iniciación (o casi debería decir inicialización) en la gestión de redes de computadores. Él fue la primera persona del grupo que conocí y la que despertó en mí el interés por la programación de sistemas distribuidos. Roberto ha hecho que mi vida fuera mucho más amena, y me ha dado ideas que resultaron de gran utilidad para mi trabajo. A Juan le tengo que agradecer, ante todo, su compañía a lo largo de todos estos años. Se puede decir que él estaba allí desde el primer momento, desde aquella tarde de julio. Juntos hemos pasado muchas aventuras. Lo más sorprendente es que siempre me ha sabido ayudar, independientemente del tipo de problema que hubiera tenido, y en parte, gracias a su ayuda esta tesis ha podido finalizarse.

Quiero agradecer también al profesor Michael O'Boyle del Institute for Computing

Systems Architecture de la Universidad de Edimburgo, por su interés mostrado en mi trabajo, así como por su asesoramiento en distintos tópicos relacionados con la paralelización de códigos irregulares.

Quiero darles las gracias a todos mis amigos que me ofrecieron su compañía y me prestaron su ayuda cuando más la necesitaba. En especial a Vladimir, por su colaboración en el diseño gráfico de esta tesis. A Emilio, con quien compartí grandes momentos en Escocia, y me ofreció la infraestructura necesaria para mantenerme comunicado y poder realizar buena parte de mi trabajo de investigación. A Álvaro, por todos los grandes momentos que hemos pasado juntos y por su carácter optimista que siempre ha sido una fuente de motivación para mí. A Olalla, por su amistad, aprecio y simpatía durante todo este tiempo. A Silvia, por su compañía a lo largo de estos años, y por todas las risas y sustos que hemos compartido.

Quiero agradecer al EPCC (Edinburgh Parallel Computing Centre), al CSC (Centro de Supercomputación Complutense) y al CESGA (Centro de Supercomputación de Galicia) por darme acceso a sus recursos de computación distribuida.

A la Xunta de Galicia por la beca predoctoral que he disfrutado durante estos años. Igualmente, al CICYT por el soporte económico dado por el proyecto TIC2001-3694-C02, a la Secretaria Xeral de I+D de Galicia por la financiación del proyecto PGIDT99-PXI20602B, al Fondo Europeo de Desarrollo Regional (FEDER) por el proyecto 1FD97-0118-C02 y al TRACS European Community Access to Research Infrastructure por el proyecto HPRI-CT-1999-00026.

A mi familia, por todo el apoyo que siempre me han dado. Ellos han tenido la paciencia necesaria para que yo pudiera realizar mi trabajo de la forma más cómoda y despreocupada.

Xa para rematar, debo engadir nestes agradecementos unhas verbas a Paula. A ela débolle moitas cousas. A parte da sua amizade e compañía, ela foi e é pra min unha referencia en canto a capacidade de traballo e esforzo persoal. Con ela compartín unha infinidade de momentos únicos, e a sua vitalidade fixo que eu poidera acadar moitas das metas propostas nesta tese.

"Y no dejamos de preguntarnos, una y otra vez, Hasta que un puñado de tierra Nos calla la boca ... Pero ¿es eso una respuesta?"

> Heinrich Heine Lazarus

## Índice General

| N  | otaci | ón                                                       | 1  |

|----|-------|----------------------------------------------------------|----|

| Pı | refac | lo .                                                     | 3  |

| 1  | Intr  | oducción                                                 | 5  |

|    | 1.1   | Arquitecturas paralelas                                  | 7  |

|    | 1.2   | Modelos de programación paralela                         | 10 |

|    | 1.3   | Herramientas de paralelización automática                | 12 |

|    | 1.4   | Códigos irregulares                                      | 15 |

|    | 1.5   | Contribución y organización de esta tesis                | 18 |

| 2  | Car   | acterización del patrón de acceso a memoria              | 25 |

|    | 2.1   | Introducción                                             | 26 |

|    | 2.2   | Trabajo previo                                           | 29 |

|    |       | 2.2.1 Caracterización de los patrones de acceso          | 30 |

|    |       | 2.2.2 Caracterización geométrica del patrón de acceso    | 33 |

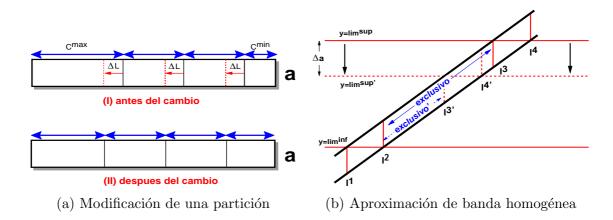

|    | 2.3   | Clasificación de las entradas de una indirección         | 35 |

|    |       | 2.3.1 Algoritmo de clasificación por <i>slices</i>       | 37 |

|    |       | 2.3.2 Algoritmo de clasificación por $slices$ modificado | 40 |

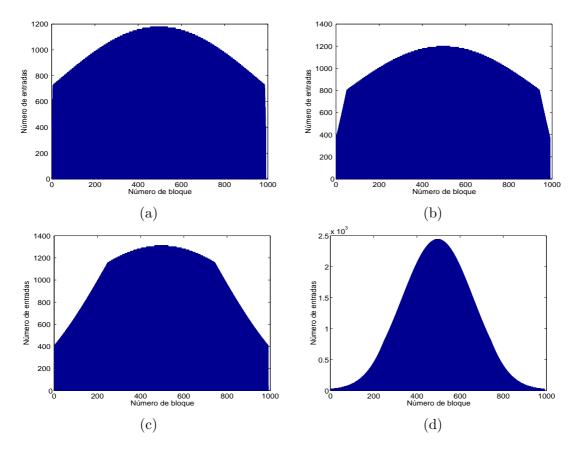

|    |       | 2.3.3 Resultados experimentales                          | 41 |

|   | 2.4            | Carac                                                    | terización geométrica de la indirección          | 43                                                 |

|---|----------------|----------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|

|   |                | 2.4.1                                                    | Algoritmo de caracterización geométrica          | 44                                                 |

|   |                | 2.4.2                                                    | Evaluación del rendimiento                       | 63                                                 |

|   | 2.5            | Carac                                                    | terización del patrón de acceso                  | 71                                                 |

|   |                | 2.5.1                                                    | Obtención de la representación IARD              | 71                                                 |

|   |                | 2.5.2                                                    | Transformación de la representación $IARD$       | 72                                                 |

|   |                | 2.5.3                                                    | Evaluación del Rendimiento                       | 76                                                 |

| 3 | Det            | ección                                                   | de dependencias                                  | 81                                                 |

|   | 3.1            | Técnie                                                   | cas de detección de dependencias de datos        | 83                                                 |

|   | 3.2            | Región                                                   | n de solape entre dos representaciones IARD      | 84                                                 |

|   | 3.3            | Algori                                                   | tmo para la determinación de la región de solape | 86                                                 |

|   | 3.4            | Consid                                                   | deraciones de eficiencia                         | 93                                                 |

|   |                |                                                          |                                                  |                                                    |

| 4 | Opt            | imizac                                                   | ción de códigos irregulares con una indirección  | 95                                                 |

| 4 | <b>Opt</b> 4.1 |                                                          | zión de códigos irregulares con una indirección  | <b>95</b><br>96                                    |

| 4 | _              |                                                          |                                                  |                                                    |

| 4 | _              | Traba                                                    | jo previo                                        | 96<br>96                                           |

| 4 | _              | Traba, 4.1.1 4.1.2                                       | jo previo                                        | 96<br>96<br>99                                     |

| 4 | 4.1            | Traba, 4.1.1 4.1.2                                       | jo previo                                        | 96<br>96<br>99<br>108                              |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale                                | jo previo                                        | 96<br>96<br>99<br>108<br>110                       |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale 4.2.1 4.2.2                    | jo previo                                        | 96<br>96<br>99<br>108<br>110<br>129                |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale 4.2.1 4.2.2                    | jo previo                                        | 96<br>96<br>99<br>108<br>110<br>129<br>157         |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale 4.2.1 4.2.2 Mejora             | jo previo                                        | 96<br>96<br>99<br>108<br>110<br>129<br>157<br>157  |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale 4.2.1 4.2.2 Mejora 4.3.1 4.3.2 | jo previo                                        | 96<br>96<br>99<br>108<br>110<br>129<br>157<br>157  |

| 4 | 4.1            | Traba, 4.1.1 4.1.2 Parale 4.2.1 4.2.2 Mejora 4.3.1 4.3.2 | jo previo                                        | 96<br>99<br>108<br>110<br>129<br>157<br>158<br>168 |

| 5 | Opt | imizac | ción de códigos irregulares con varias indirecciones     | 183 |

|---|-----|--------|----------------------------------------------------------|-----|

|   | 5.1 | Introd | lucción                                                  | 184 |

|   | 5.2 | Traba  | jo previo                                                | 187 |

|   |     | 5.2.1  | Ejecución especulativa                                   | 187 |

|   |     | 5.2.2  | Estrategia Inspector-Ejecutor                            | 188 |

|   | 5.3 | Algori | itmo CYT                                                 | 190 |

|   |     | 5.3.1  | Fase de inspección del algoritmo CYT                     | 190 |

|   |     | 5.3.2  | Fase de ejecución del algoritmo CYT                      | 192 |

|   |     | 5.3.3  | Análisis de eficiencia                                   | 194 |

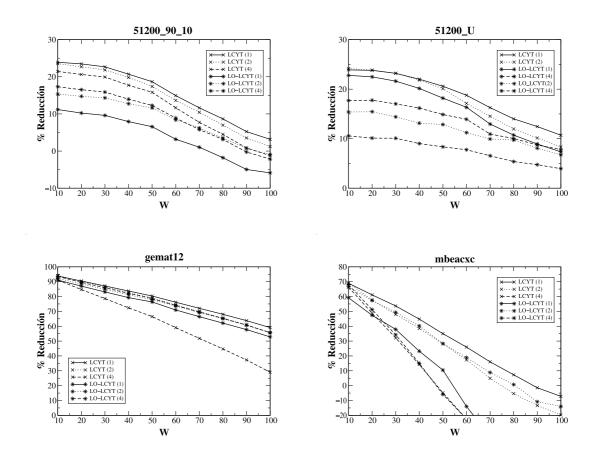

|   | 5.4 | Algori | itmos LCYT y LO-LCYT                                     | 195 |

|   |     | 5.4.1  | Fase de inspección del algoritmo LCYT                    | 195 |

|   |     | 5.4.2  | Fase de inspección del algoritmo LO-LCYT                 | 197 |

|   |     | 5.4.3  | Fase de ejecución                                        | 199 |

|   |     | 5.4.4  | Evaluación del rendimiento                               | 199 |

|   | 5.5 | Uso d  | el IARD para la mejora del rendimiento                   | 210 |

|   |     | 5.5.1  | Representación IARD de dos indirecciones                 | 210 |

|   |     | 5.5.2  | Ejecutor paralelo                                        | 213 |

|   |     | 5.5.3  | Análisis de eficiencia                                   | 213 |

|   | 5.6 | Algori | itmos OWNCR y SLCSRT                                     | 215 |

|   |     | 5.6.1  | Estrategia OWNCR                                         | 217 |

|   |     | 5.6.2  | Estrategia SLCSRT                                        | 218 |

|   |     | 5.6.3  | Balanceo de carga                                        | 223 |

|   |     | 5.6.4  | Análisis de eficiencia                                   | 224 |

|   |     | 5.6.5  | Mejoras de la estrategia SLCSRT                          | 235 |

| 6 | Opt | imizac | ción de códigos irregulares con operaciones de reducción | 241 |

|   | 6.1 |        | ijo previo                                               | 242 |

|   | 6.2                 | Algori                                     | tmo básico de clasificación por slices           | 249                        |

|---|---------------------|--------------------------------------------|--------------------------------------------------|----------------------------|

|   |                     | 6.2.1                                      | Estructura del inspector-ejecutor                | 249                        |

|   |                     | 6.2.2                                      | Análisis de eficiencia                           | 252                        |

|   | 6.3                 | Algori                                     | tmo avanzado de clasificación por slices         | 255                        |

|   |                     | 6.3.1                                      | Esquema de almacenamiento                        | 255                        |

|   |                     | 6.3.2                                      | Estructura del ejecutor                          | 259                        |

|   |                     | 6.3.3                                      | Estructura del inspector                         | 265                        |

|   |                     | 6.3.4                                      | Estructura del $scheduler$                       | 268                        |

|   |                     | 6.3.5                                      | Resultados                                       | 271                        |

|   | 6.4                 | Parale                                     | elización del inspector SLCCLS                   | 284                        |

|   |                     | 6.4.1                                      | Análisis de eficiencia                           | 288                        |

|   |                     | 0.1.1                                      |                                                  | 200                        |

| 7 | Árb                 |                                            | decisión                                         | 291                        |

| 7 | <b>Á</b> rb         | ool de                                     |                                                  | 291                        |

| 7 |                     | ool de d<br>Traba                          | decisión                                         | <b>291</b> 292             |

| 7 | 7.1                 | ool de d<br>Traba                          | <b>decisión</b><br>jo previo                     | <b>291</b> 292 292         |

| 7 | 7.1                 | Traba<br>Estruc                            | decisión  jo previo  ctura del árbol de decisión | <b>291</b> 292 292 296     |

| 7 | 7.1                 | Traba<br>Estruc<br>7.2.1                   | decisión  jo previo                              | <b>291</b> 292 292 296 298 |

|   | 7.1<br>7.2          | Traba<br>Estruc<br>7.2.1<br>7.2.2<br>7.2.3 | decisión  jo previo                              | <b>291</b> 292 292 296 298 |

| C | 7.1<br>7.2<br>onclu | Traba<br>Estruc<br>7.2.1<br>7.2.2<br>7.2.3 | decisión  jo previo                              | <b>291</b> 292 296 298 300 |

## Índice de Tablas

| 2.1  | Eficiencia de los algoritmos CS y CSM                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Estructura de datos asociada a un segmento de $\mathcal{C}$                                                                |

| 2.3  | Ejemplo de accesos para un lazo tipo B                                                                                     |

| 2.4  | Eficiencia de la representación IARD                                                                                       |

| 2.5  | Tiempo de cálculo $(ms)$ de la representación IARD                                                                         |

| 3.1  | Ejemplo de Valores de $s_i^{min}$ y $s_i^{max}$                                                                            |

| 4.1  | Criterio de selección para la obtención de los $slices$ asociados a una partición.113                                      |

| 4.2  | Tipos de redondeo para la función interseca                                                                                |

| 4.3  | Características de las matrices struct3 y diag_block                                                                       |

| 4.4  | Coste de la representación IARD y del inspector de la estrategia PRT 122                                                   |

| 4.5  | Técnica más eficiente para distintos valores de $N_x$ y $\lambda$ para $N_p=8.$ 128                                        |

| 4.6  | Características del conjunto de matrices dispersas y tiempo de caracterización IARD (en $ms$ ) empleando el algoritmo CSM  |

| 4.7  | Tiempos de ejecución del ejecutor para 8 procesadores (en $ms$ ) 149                                                       |

| 4.8  | Tiempos de ejecución del ejecutor para 8 procesadores (en $ms$ ) 149                                                       |

| 4.9  | Tiempo de ejecución con 10 procesadores para matrices sintéticas (en $ms$ ) para la reducción irregular                    |

| 4.10 | Tiempo de ejecución con 10 procesadores para matrices sintéticas (en <i>ms</i> )  para el producto matriz dispersa vector. |

| 4.11 | Tiempo de ejecución con 10 procesadores para matrices sintéticas (en $ms$ ) para la transposición de una matriz dispersa |

|------|--------------------------------------------------------------------------------------------------------------------------|

| 4.12 | Tiempo de ejecución de los inspectores DWA-LIP y SPRT (en $ms$ ) 152                                                     |

| 4.13 | Tiempo de ejecución de los inspectores DWA-LIP y SPRT (en $ms$ ) 152                                                     |

| 4.14 | Umbral (en iteraciones) para sobrepasar el rendimiento del código secuencial.156                                         |

| 4.15 | Tiempo de ejecución del inspector para distintos particionamientos $(ms)$ 167                                            |

| 4.16 | Tiempo de ejecución del particionador para 3 particiones                                                                 |

| 4.17 | Relación de mejora para la reducción irregular con $N_{pt}=3.$                                                           |

| 4.18 | Comparación entre la precisión del resultado óptimo y heurístico 179                                                     |

| 4.19 | Comparación entre la precisión del resultado óptimo y heurístico 179                                                     |

| 4.20 | Eficiencia del inspector para distintos particionamientos ( $\sigma=2$ ) 181                                             |

| 4.21 | Eficiencia del inspector para distintos particionamientos ( $\sigma=6$ ) 181                                             |

| 5.1  | Características de las matrices de prueba                                                                                |

| 5.2  | Balanceo de carga de las estrategias LCYT y LO-LCYT                                                                      |

| 5.3  | Umbral de iteraciones para superar la estrategia CYT 209                                                                 |

| 5.4  | Eficiencia de la clasificación por <i>slices</i> para $N_{stmt}=2$ con distintos patrones de acceso                      |

| 5.5  | Eficiencia de técnica SLCSRT con distintos patrones de acceso                                                            |

| 5.6  | Patrones de acceso utilizados para el código de prueba sintético 230                                                     |

| 5.7  | Umbral de iteraciones para que la estrategia SLCSRT supere al resto de las propuestas                                    |

| 5.8  | Patrones de acceso utilizados y aceleraciones obtenidas para el código de prueba PLTMG                                   |

| 5.9  | Patrones de acceso utilizados y aceleraciones obtenidas para el código de prueba BDNA                                    |

| 5.10 | Eficiencia de la técnica SLCSRT-LP con distintos patrones de acceso 236                                                  |

| 6.1  | Eficiencia de la clasificación por <i>slices</i> para SLCCL con distintos patrones de acceso                                    |  |

|------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 6.2  | Eficiencia de la clasificación por <i>slices</i> para $N_{stmt}=2$ y $N_p=4$ con distintos patrones de acceso                   |  |

| 6.3  | Eficiencia de la clasificación por <i>slices</i> para $N_{stmt}=2$ y $N_p=64$ con distintos patrones de acceso                  |  |

| 6.4  | Características de los patrones de acceso                                                                                       |  |

| 6.5  | Distribución de las iteraciones para la estrategia SLCCLS                                                                       |  |

| 6.6  | Umbral de iteraciones para 32 procesadores                                                                                      |  |

| 6.7  | Umbral de iteración de la estrategia SLCCLS con $N_p=32.\dots 283$                                                              |  |

| 6.8  | Umbral de iteración de la estrategia SLCCLS con $N_p=32.\dots\dots 283$                                                         |  |

| 6.9  | Eficiencia del inspector paralelo para distintas estrategias de distribución de las iteraciones para $prueba1$ con $iter=2000.$ |  |

| 6.10 | Eficiencia del ejecutor para $N_p=8$ con distintos valores de $N_{th}$ 289                                                      |  |

| 6.11 | Tiempos de ejecución y aceleraciones para el inspector paralelo para $N_p=8$ con distintos valores de $N_{th}$                  |  |

| A.1  | Latencia de acceso asociada al MIPS R10000                                                                                      |  |

# Índice de Figuras

| 1.1  | Ejemplos de lazos irregulares con una indirección                                | 16 |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Ejemplos de lazos irregulares con varias indirecciones                           | 17 |

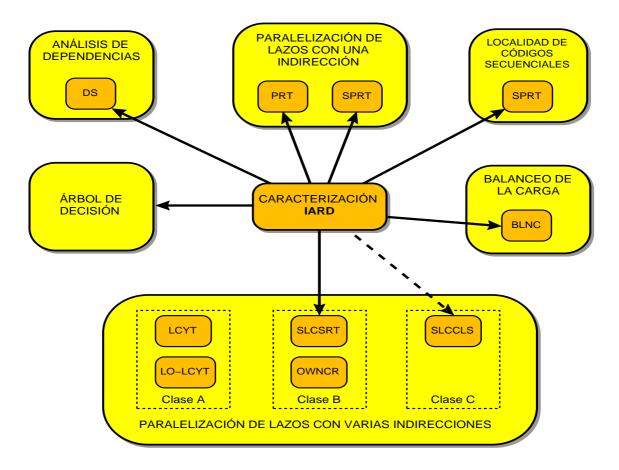

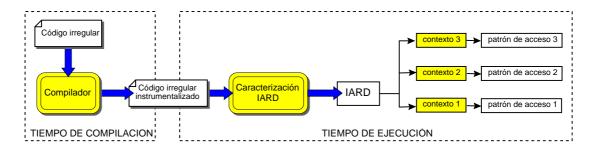

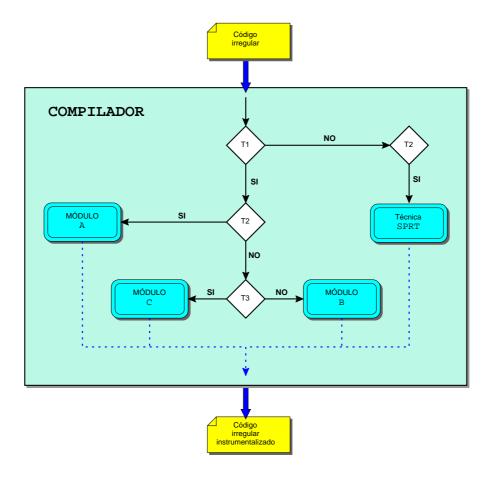

| 1.3  | Estructura general de nuestra contribución                                       | 20 |

| 2.1  | Ejemplos de accesos por medio de una indirección                                 | 27 |

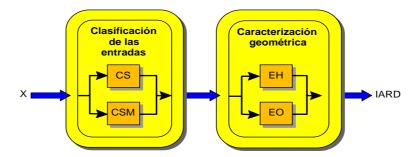

| 2.2  | Esquema de caracterización de una indirección                                    | 28 |

| 2.3  | Ejemplo de lazo regular doblemente anidado                                       | 30 |

| 2.4  | Ejemplo de lazo considerado                                                      | 36 |

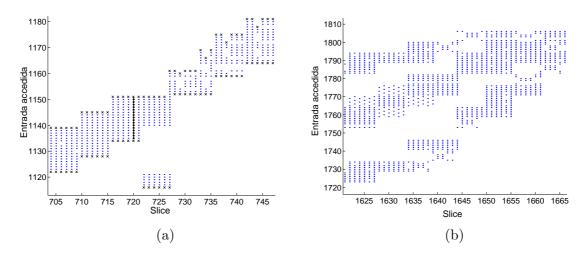

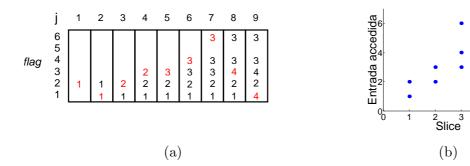

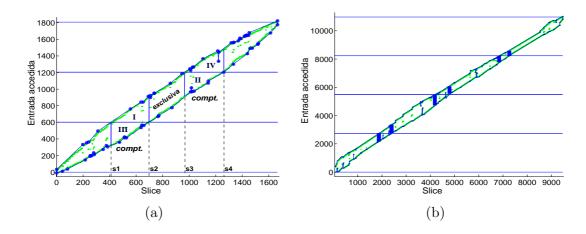

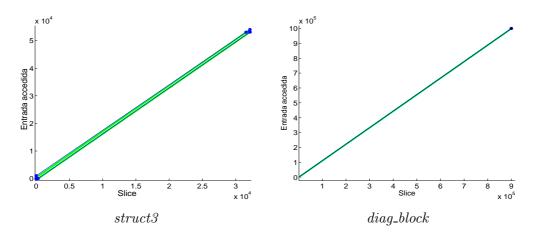

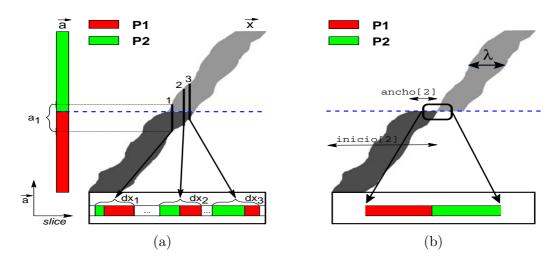

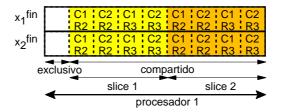

| 2.5  | Representación por slices                                                        | 37 |

| 2.6  | Algoritmo de clasificación por $slices$ (CS)                                     | 39 |

| 2.7  | Ejemplo del funcionamiento del algoritmo CS                                      | 40 |

| 2.8  | Ejemplos de códigos irregulares                                                  | 40 |

| 2.9  | Algoritmo de clasificación por $slices$ modificado (CSM)                         | 42 |

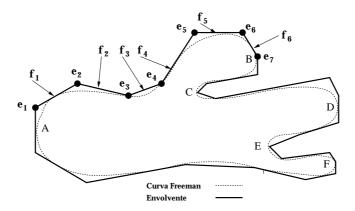

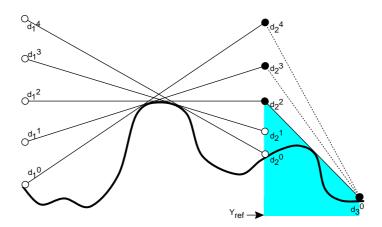

| 2.10 | Ejemplo de envolvente a una curva                                                | 46 |

| 2.11 | Puntos asociados a un segmento de $\mathcal{C}.$                                 | 48 |

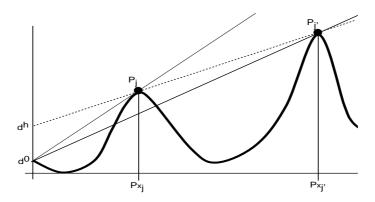

| 2.12 | Determinación del valor del parámetro $h.$                                       | 50 |

| 2.13 | Pseudocódigo del algoritmo PNT_TNG                                               | 52 |

| 2.14 | Pseudocódigo del algoritmo TBL_TNG                                               | 53 |

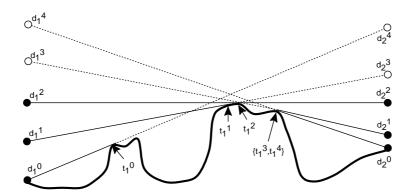

| 2.15 | Representación gráfica de los campos $d_i$ y $d_{i+1}$ de una tabla de tangencia | 54 |

| 2.16 | Uniones posibles de $d_3^0$ con $d_2$                                            | 55 |

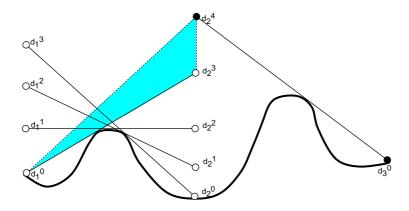

| 2.17 | Algoritmo envolvente óptima EO                                                                           | 57  |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 2.18 | Nuevo nivel en $d_2$ debido al punto $d_3^0$                                                             | 58  |

| 2.19 | Algoritmo envolvente heurística EH                                                                       | 61  |

| 2.20 | Efecto del incremento en $y_i$                                                                           | 62  |

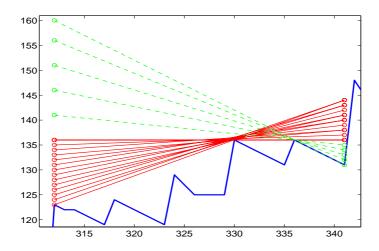

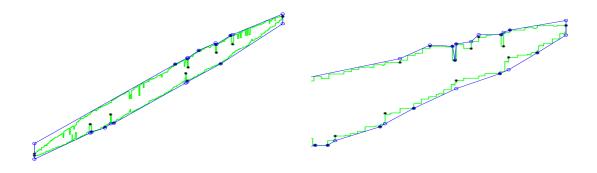

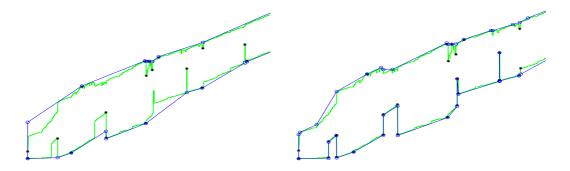

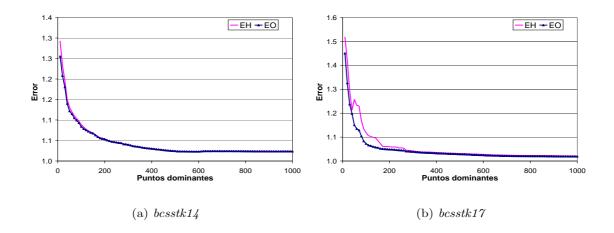

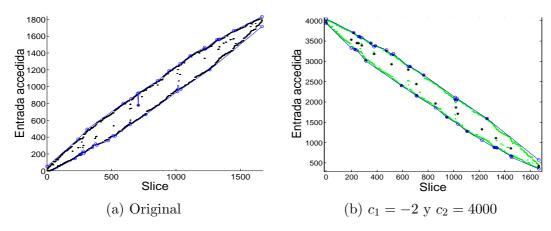

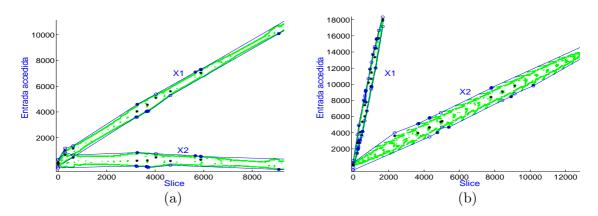

| 2.21 | Curvas asociadas a la matriz bcsstk14                                                                    | 64  |

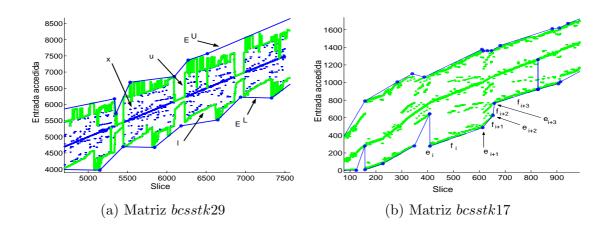

| 2.22 | Curvas asociadas a la matriz bcsstk17                                                                    | 65  |

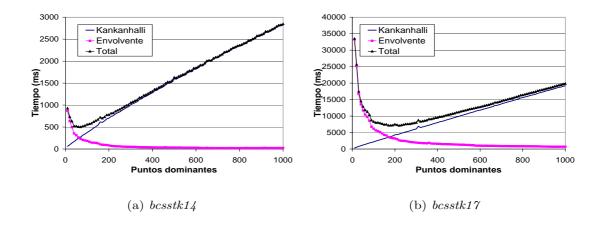

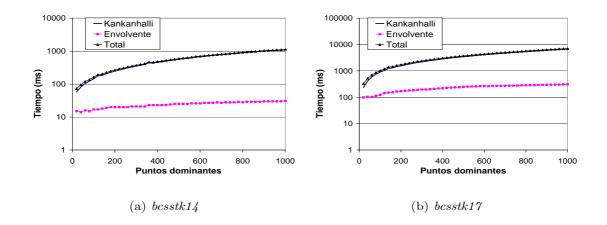

| 2.23 | Tiempos de ejecución del algoritmo EO                                                                    | 65  |

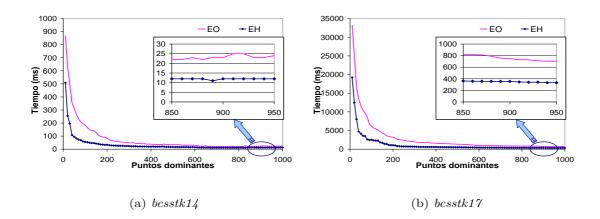

| 2.24 | Tiempos de ejecución del cálculo de la envolvente para ambas propuestas                                  | 66  |

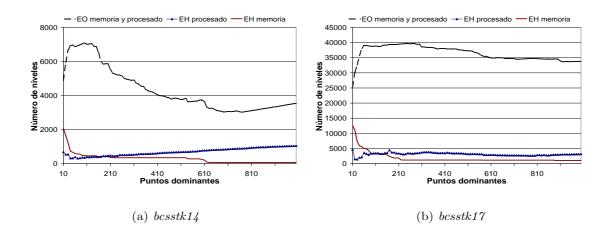

| 2.25 | Eficiencia de ambas propuestas                                                                           | 67  |

| 2.26 | Factores de error                                                                                        | 67  |

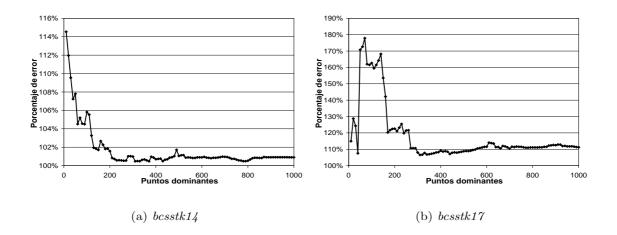

| 2.27 | Porcentaje de diferencia de errores                                                                      | 68  |

| 2.28 | Ejemplo de operación por desplazamiento por slice                                                        | 69  |

| 2.29 | Tiempos de ejecución del algoritmo EH con un patrón de acceso cuya pendiente asociada es próxima a cero. | 70  |

| 2.30 | Procedimiento de caracterización de una indirección                                                      | 71  |

| 2.31 | Ejemplo de estructuras irregulares                                                                       | 72  |

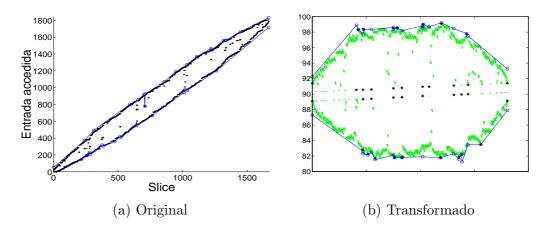

| 2.32 | Ejemplos de transformación en el patrón de acceso                                                        | 75  |

| 2.33 | Representación por slices                                                                                | 77  |

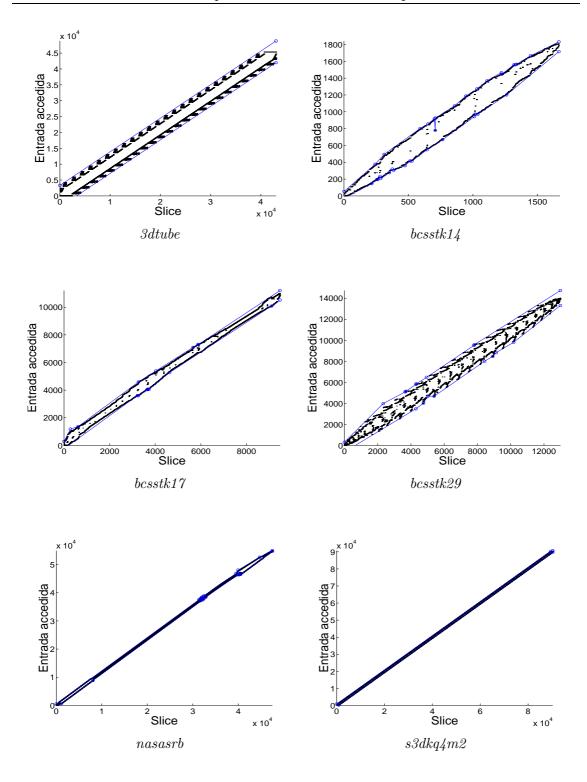

| 2.34 | Patrón de acceso y representación IARD de diversas indirecciones                                         | 78  |

| 3.1  | Ejemplos de secciones de código irregular                                                                | 82  |

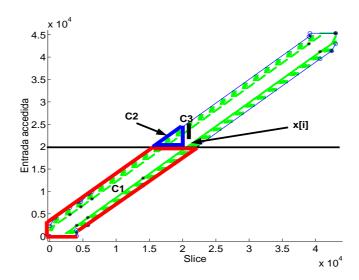

| 3.2  | Ejemplos de cálculo de la región de solape entre dos representaciones IARD.                              | 84  |

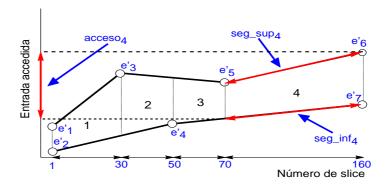

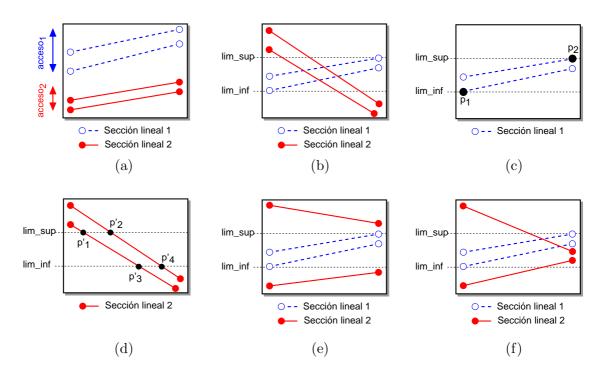

| 3.3  | Descomposición en secciones lineales de una representación IARD                                          | 87  |

| 3.4  | Algoritmo de determinación de solape (algoritmo DS) entre dos representaciones IARD.                     | 89  |

| 3.5  | Ejemplos de cálculo de la región de solape entre dos representaciones IARD.                              | 91  |

| 4.1  | Ejemplos de código irregular con una única indirección                                                   | 100 |

| 4.2 Ejemplos de paralelización mediante primitivas de sincronización 101                |

|-----------------------------------------------------------------------------------------|

| 4.3 Ejemplos de paralelización mediante privatización                                   |

| 4.4 Paralelización mediante la aplicación de regla del propietario mediante sen-        |

| tencias condicionales                                                                   |

| 4.5 Paralelización mediante la técnica de LOCALWRITE                                    |

| 4.6 Paralelización mediante la técnica de DWA-LIP                                       |

| 4.7 Ejemplos de códigos irregulares                                                     |

| 4.8 Ejemplo de lazo irregular paralelo, con ejecución guiada por <i>slices</i> 109      |

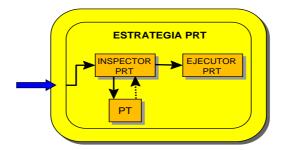

| 4.9 Estructura de la estrategia PRT                                                     |

| 4.10 Ejemplos de esquemas de particionamiento                                           |

| 4.11 Algoritmo de particionamiento (PT)                                                 |

| 4.12 Código ejecutor de la estrategia PRT                                               |

| 4.13 Organización de las entradas para una región compartida 117                        |

| 4.14 Pseudocódigo del inspector PRT                                                     |

| $4.15$ Reordenamiento de las entradas de un $\it slice$ por medio del algoritmo PRT 119 |

| 4.16 Patrón de acceso y representación IARD de diversas indirecciones 122               |

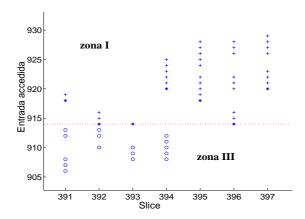

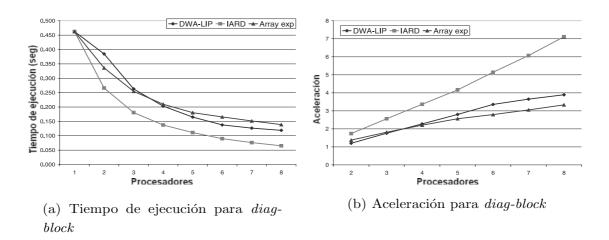

| 4.17 Rendimiento obtenido para la matriz diag-block                                     |

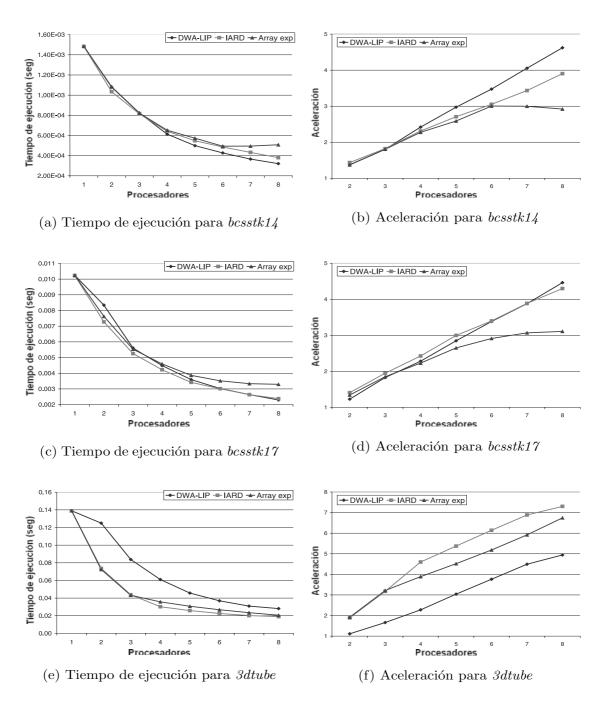

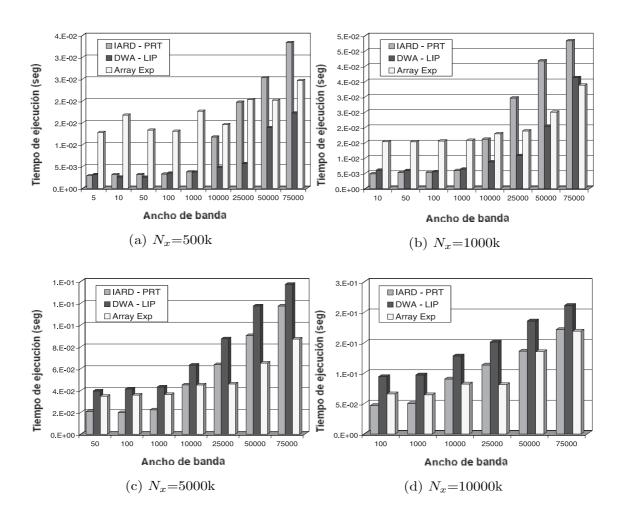

| 4.18 Rendimiento obtenido para las matrices bcsstk14, bcsstk17 y 3dtube 124             |

| 4.19 Rendimiento obtenido para las matrices $nasasrb$ , $s3dkq4m2$ y $struct3$ 125      |

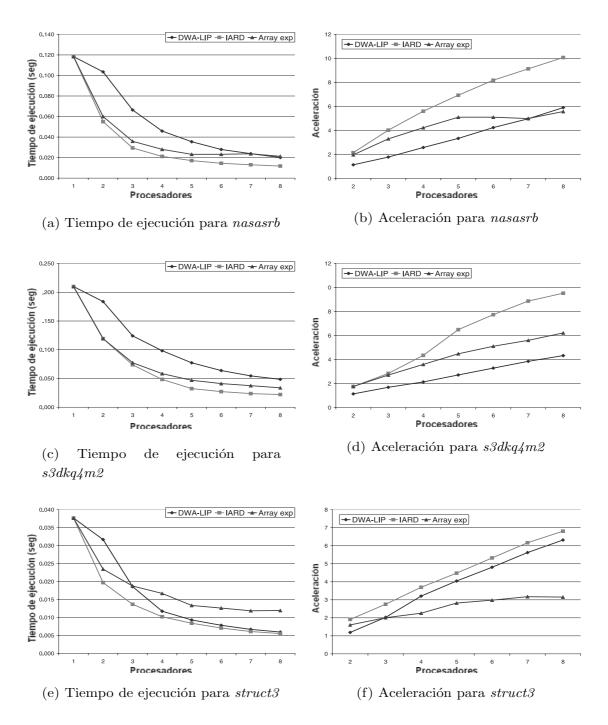

| 4.20 Representación IARD de matrices sinteticas                                         |

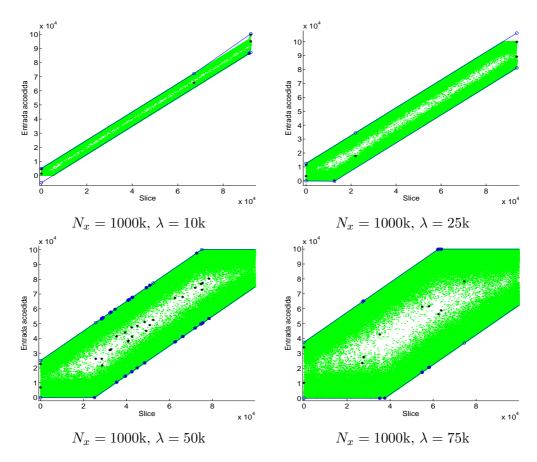

| 4.21 Rendimiento para las matrices sintéticas para $N_p=8.$                             |

| 4.22 Distribución de entradas de un patrón de acceso                                    |

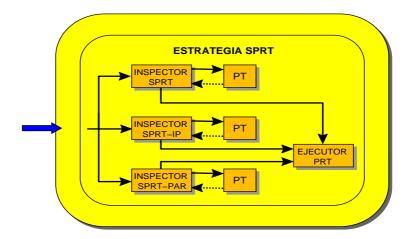

| 4.23 Estructura de la estrategia SPRT                                                   |

| 4.24 Algoritmo inspector Sorted Private Region Technique (SPRT) 132                     |

| 4.25 Algoritmo inspector Sorted Private Region Technique in Place (SPRT-IP) 136         |

| 4.26 Ejemplo de las contribuciones a la nueva posición de cada punto 137                |

|                                                                                         |

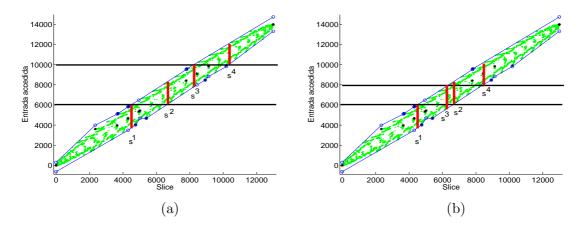

| 4.27 | Distintos particionamientos para la representación IARD extraída de la matriz bcsstk29 |

|------|----------------------------------------------------------------------------------------|

| 4.28 | Algoritmo inspector Sorted Private Region Technique paralelo (SPRT-PAR). 142           |

| 4.29 | Código ejecutor de la estrategia SPRT                                                  |

| 4.30 | Reducción irregular                                                                    |

| 4.31 | Rutina <i>spmxv</i>                                                                    |

| 4.32 | Rutina <i>csrcsc2</i>                                                                  |

| 4.33 | Algoritmo interseca2                                                                   |

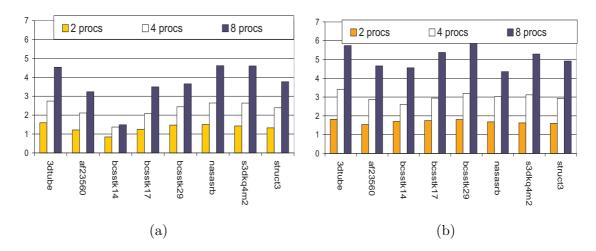

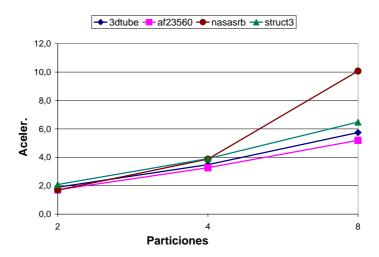

| 4.34 | Aceleraciones obtenidas para el algoritmo SPRT paralelo                                |

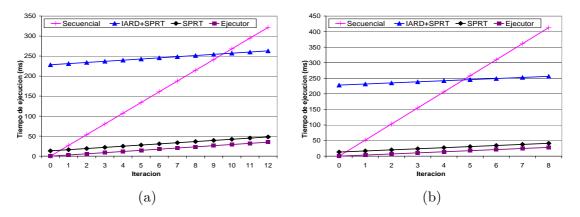

| 4.35 | Tiempo de ejecución (en $ms$ ) para la matriz $bcsstk17.$                              |

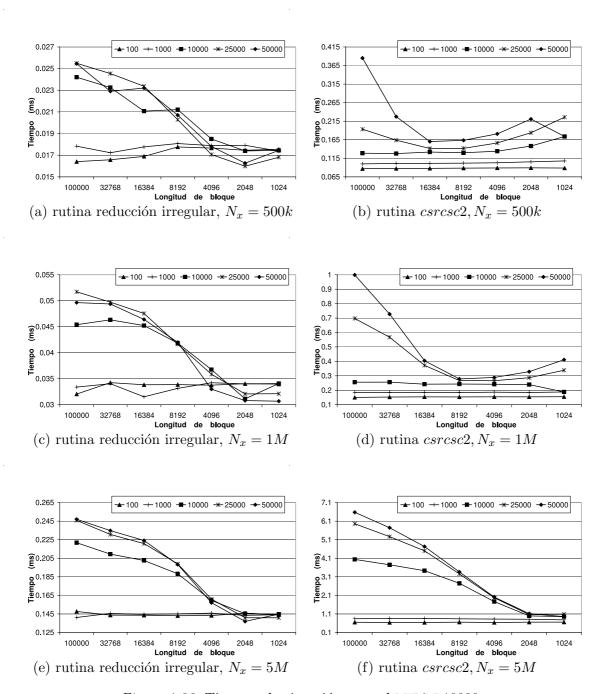

| 4.36 | Tiempos de ejecución para el MIPS R10000                                               |

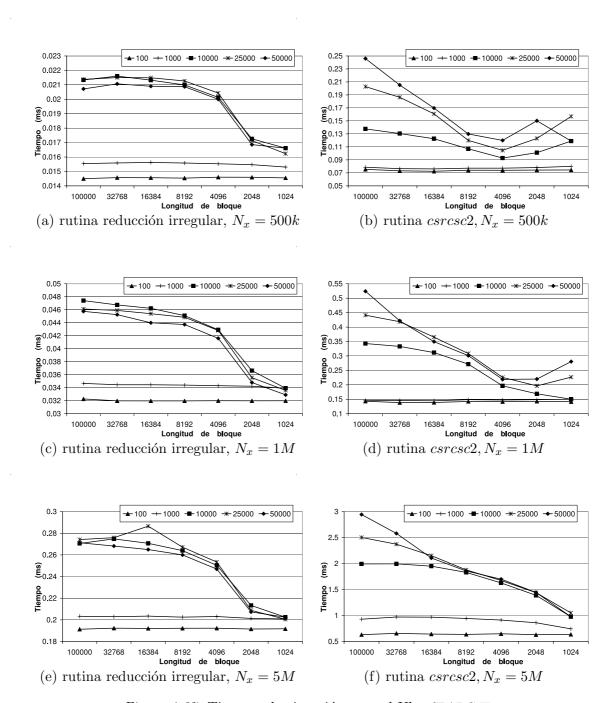

| 4.37 | Tiempos de ejecución para el UltraSPARC II                                             |

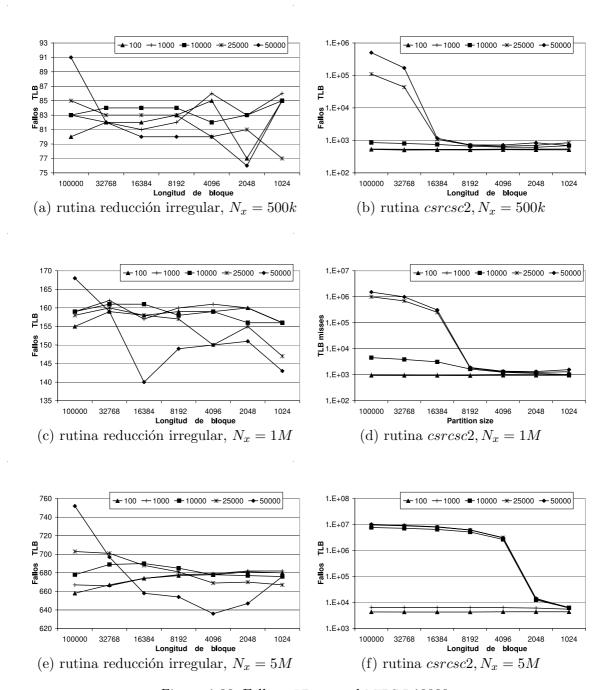

| 4.38 | Fallos TLB para el MIPS R10000                                                         |

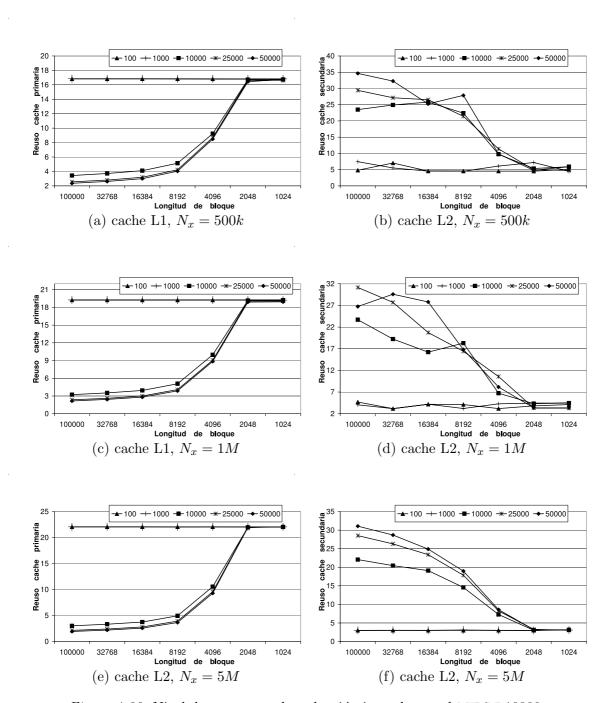

| 4.39 | Nivel de reuso para la reducción irregular en el MIPS R10000                           |

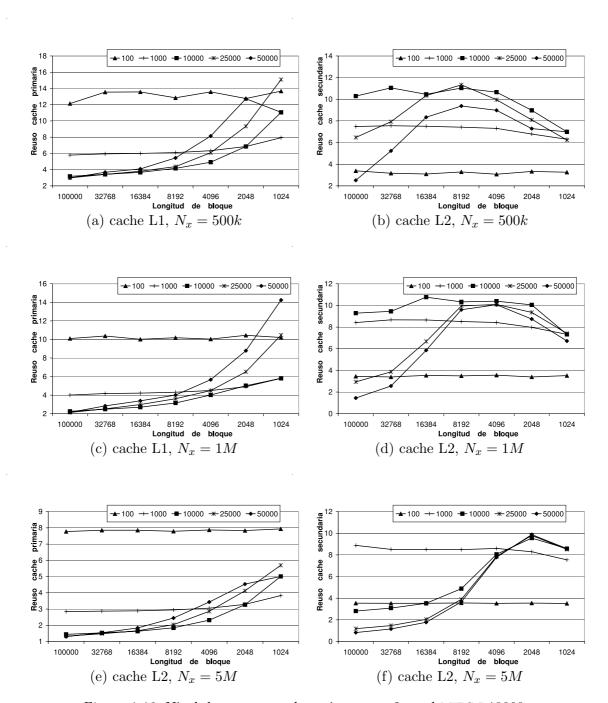

| 4.40 | Nivel de reuso para la rutina $csrcsc2$ en el MIPS R10000                              |

| 4.41 | Reducción irregular                                                                    |

| 4.42 | Representación de solape entre regiones compartidas                                    |

| 4.43 | Algoritmo para balanceo de la carga (BLNC)                                             |

| 4.44 | Esquemas de partición empleando la representación IARD                                 |

| 4.45 | Histograma de accesos para matrices sintéticas desbalanceadas 180                      |

| 5.1  | Ejemplos de lazos irregulares con varias indirecciones                                 |

| 5.2  | Ejemplo de lazo irregular                                                              |

| 5.3  | Ejemplo de vectores de indirección                                                     |

| 5.4  | Ejemplo de <i>ticket table</i>                                                         |

| 5.5  | Inspector secuencial de la estrategia CYT                                              |

| 5.6  | Ejecutor paralelo del algoritmo CYT                                                    |

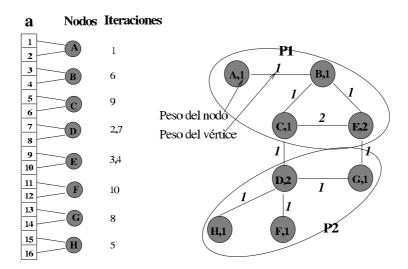

| 5.7  | Representación del patrón de acceso mediante un grafo                                  |

|------|----------------------------------------------------------------------------------------|

| 5.8  | Ejecutor paralelo de los algoritmos LCYT y LO-LCYT                                     |

| 5.9  | Código irregular de prueba                                                             |

| 5.10 | Porcentaje de reducción en el tiempo de ejecución para 8 procesadores. $$ 203          |

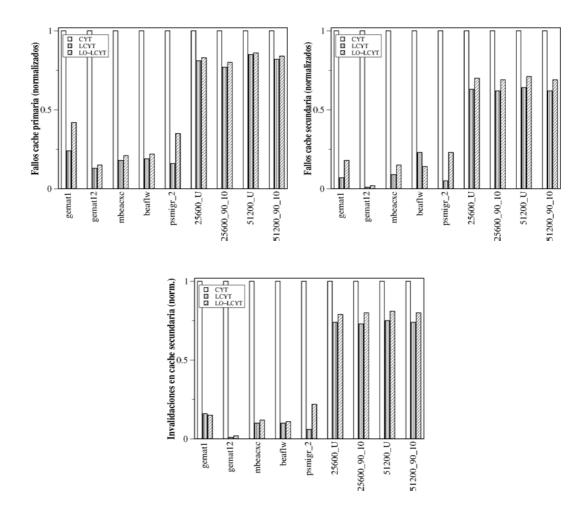

| 5.11 | Rendimiento a nivel de memoria cache de las tres estrategias 205                       |

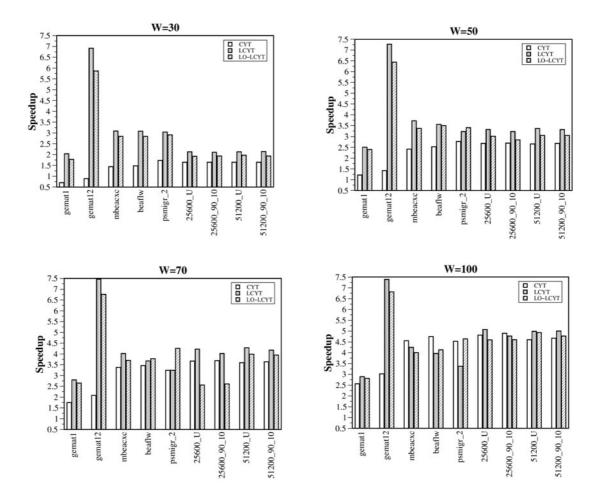

| 5.12 | Aceleraciones obtenidas con 8 procesadores para diferentes cargas de trabajo.207       |

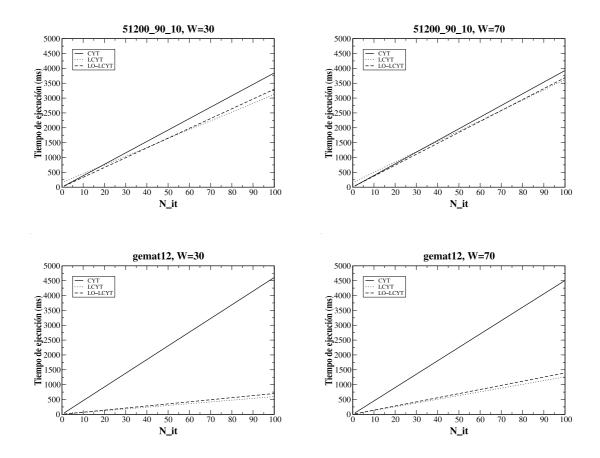

| 5.13 | Tiempo total de ejecución para 8 procesadores                                          |

| 5.14 | Pseudocódigo del algoritmo de clasificación por $slices$ de varias indirecciones (CS3) |

| 5.15 | Ejecutor paralelo para una representación por $slices$ de dos indirecciones 213        |

| 5.16 | Algoritmo de generación de indirecciones                                               |

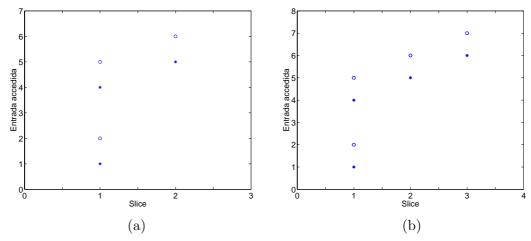

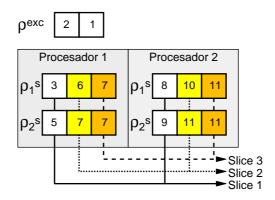

| 5.17 | Resultado del algoritmo de clasificación por <i>slices</i>                             |

| 5.18 | Código paralelo para la regla del propietario                                          |

| 5.19 | Pseudocódigo del inspector paralelo del algoritmo SLCSRT                               |

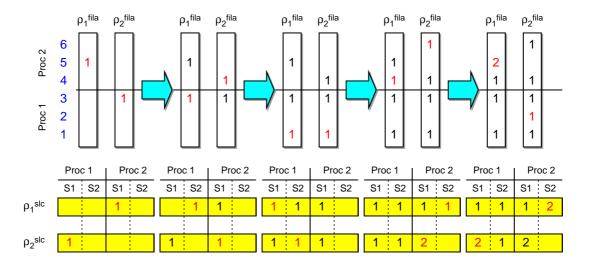

| 5.20 | Secuencia de valores de los vectores $\rho^{slc}$ y $\rho^{fila}$                      |

| 5.21 | Operación de desplazamiento sobre los vectores $\rho_k^{slc}$                          |

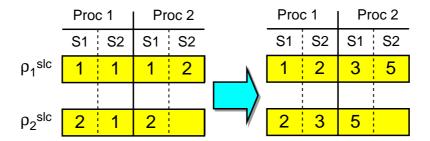

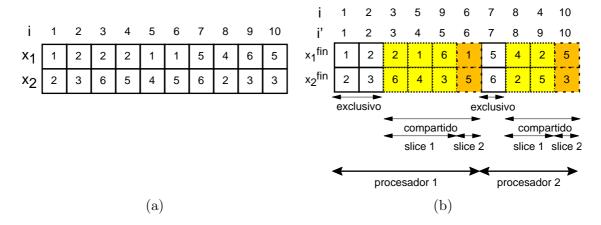

| 5.22 | Distribución de los vectores de indirección reordenados                                |

| 5.23 | Ejecutor paralelo del algoritmo SLCSRT                                                 |

| 5.24 | Algoritmo de balanceo de la carga BALANC                                               |

| 5.25 | Ejemplo de código irregular                                                            |

| 5.26 | Resultado del algoritmo de clasificación por $slices$ SLCSRT                           |

| 5.27 | Código de prueba sintético                                                             |

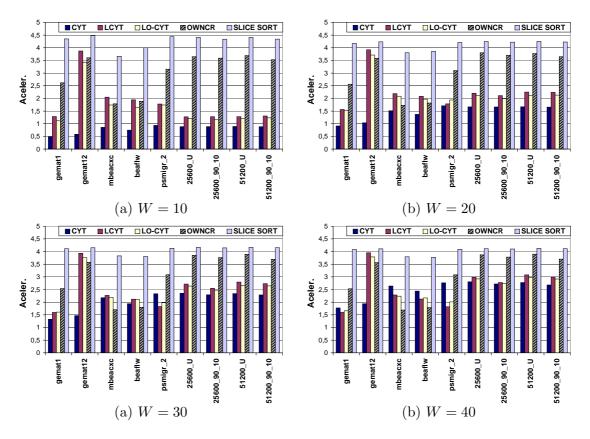

| 5.28 | Aceleraciones obtenidas para diferentes cargas de trabajo con 8 procesadores.231       |

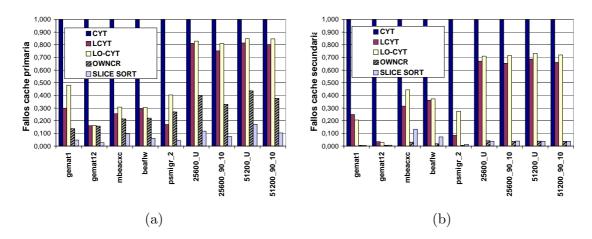

| 5.29 | Fallos en memoria cache para 8 procesadores con $W=10.$                                |

| 5.30 | Ejemplos de lazos irregulares reales                                                   |

| 5.31 | Pseudocódigo del inspector paralelo con lecturas paralelas (SLCSRT-LP) 237             |

| 5.32 | Resultado del algoritmo SLCSRT-LP                                                                     |

|------|-------------------------------------------------------------------------------------------------------|

| 5.33 | Aceleraciones obtenidas con el inspector paralelo empleando la representación IARD                    |

| 6.1  | Lazo irregular de n-cuerpos                                                                           |

| 6.2  | Pseudocódigo del inspector secuencial de la técnica DWA-LIP 244                                       |

| 6.3  | Ejecutor para la paralelización mediante la técnica DWA-LIP 245                                       |

| 6.4  | Esquema de ejecución para la técnica DWA-LIP y LOCALWRITE 246                                         |

| 6.5  | Paralelización mediante la técnica de LOCAL-WRITE                                                     |

| 6.6  | Algoritmo básico de clasificación por $slices$ (SLCCL)                                                |

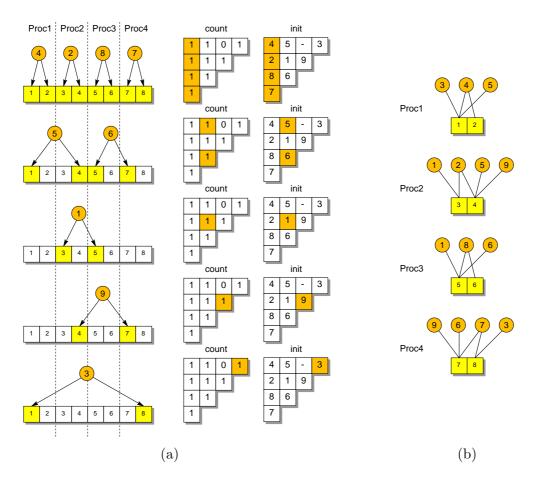

| 6.7  | Ejemplo de generación del patrón de acceso a memoria                                                  |

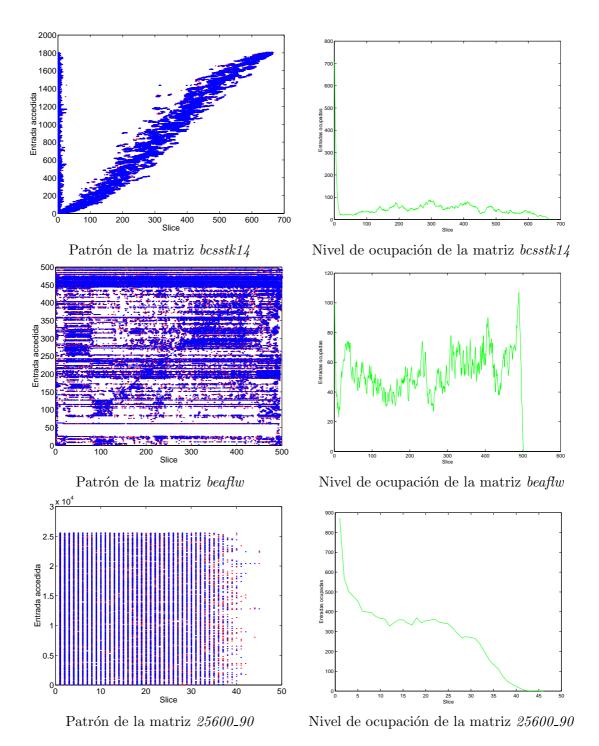

| 6.8  | Ejecutor paralelo asociado al algoritmo SLCCL                                                         |

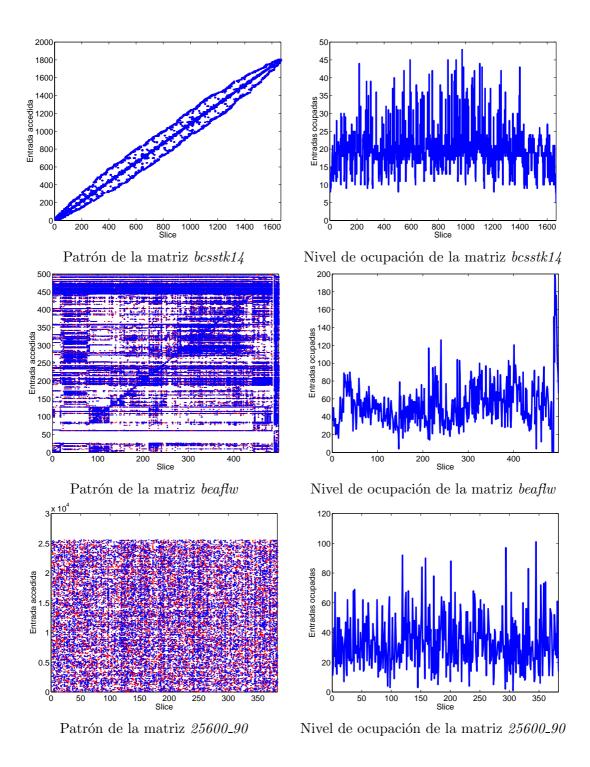

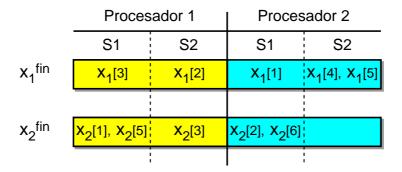

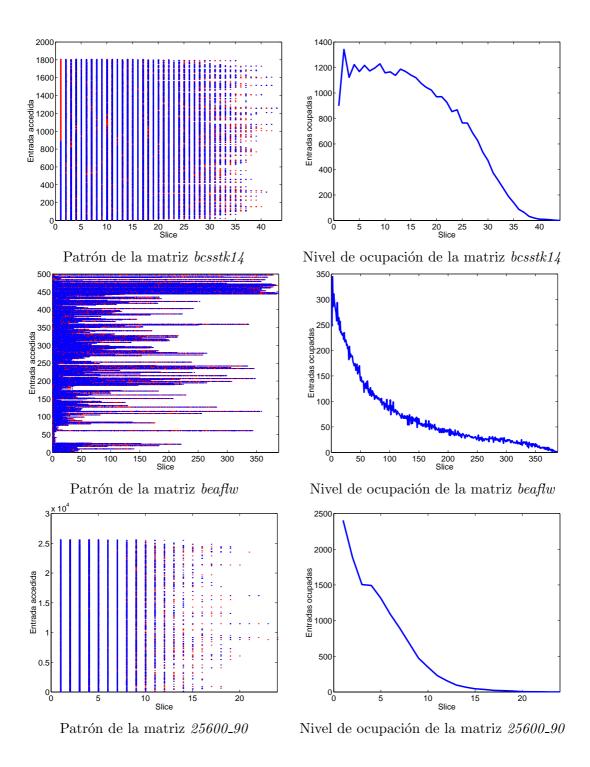

| 6.9  | Patrón de acceso asociado al algoritmo SLCCL para las matrices $bcsstk14$ , $beaflw$ y $25600$ – $90$ |

| 6.10 | Ejemplo de vectores de indirección                                                                    |

| 6.11 | Distribución de las entradas del vector de indirección para el procesador 1 con $N_p=3$               |

| 6.12 | Algoritmo ejecutor SLCCLS                                                                             |

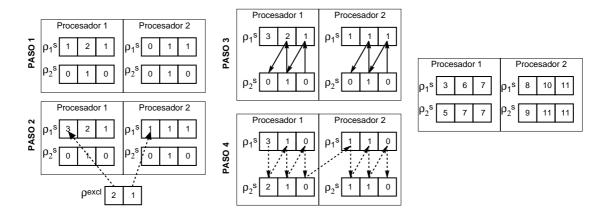

| 6.13 | Ejemplo de valores de los vectores de densidad                                                        |

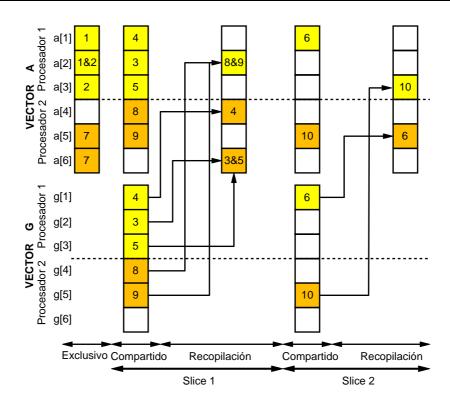

| 6.14 | Diagrama de acceso a los vectores $a$ y $g$                                                           |

| 6.15 | Algoritmo inspector SLCCLS                                                                            |

| 6.16 | Ejemplo de fase de desplazamiento                                                                     |

| 6.17 | Algoritmo scheduler                                                                                   |

| 6.18 | Ejemplo de funcionamiento del <i>scheduler</i>                                                        |

| 6.19 | Lazo irregular de n-cuerpos                                                                           |

| 6.20 | Patrón de acceso a memoria para el escenario prueba3                                                  |

| 6.21 | Tiempos de ejecución y aceleraciones con $N_p=32\ldots 276$                                           |

| 6.22 | Lazo irregular de n-cuerpos con carga de trabajo variable                                             |

| 6.23 | Tiempos de ejecución y aceleraciones para el escenario $prueba3$ con $N_p=8$ y diferentes valores de $W.$                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.24 | Distribución de las iteraciones para el inspector SLCCLS paralelo 285                                                                                                                                                               |

| 6.25 | Secuencia de entradas accedidas por el procesador 1, para $N_x=12,N_{th}=2$ y $N_{i1}=4.\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ |

| 6.26 | Algoritmo ejecutor modificado para un inspector paralelo                                                                                                                                                                            |

| 7.1  | Árbol de decisión del esquema general                                                                                                                                                                                               |

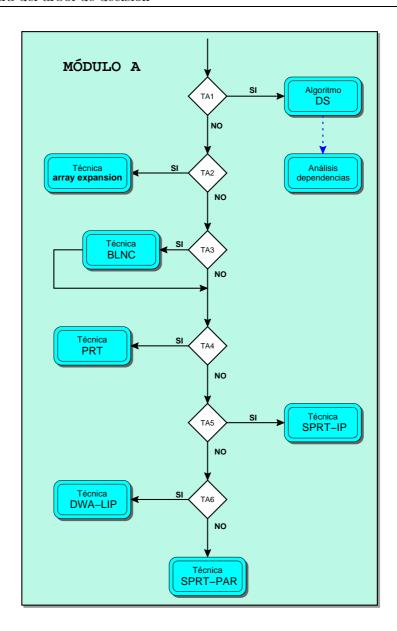

| 7.2  | Árbol de decisión del Módulo A                                                                                                                                                                                                      |

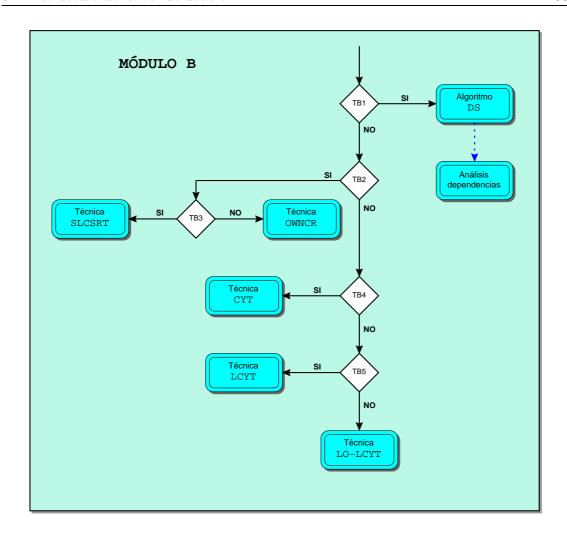

| 7.3  | Árbol de decisión del Módulo B                                                                                                                                                                                                      |

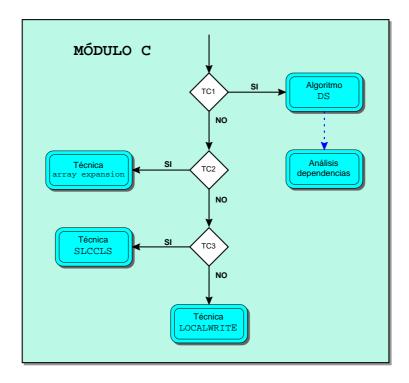

| 7.4  | Árbol de decisión del Módulo C                                                                                                                                                                                                      |

## Notación

| Símbolo                             | Significado                                                                        |

|-------------------------------------|------------------------------------------------------------------------------------|

| $\mathcal{A}_i$                     | Conjunto de entradas de $a$ pertenecientes a la partición i-ésima                  |

| a                                   | Vector de accesos                                                                  |

| $\mathcal C$                        | Curva Freeman chain-code                                                           |

| CC                                  | Camino crítico de un lazo irregular                                                |

| col                                 | Vector de distribución por columnas de una matriz dispersa                         |

| $\mathcal{CT}$                      | Conjunto de carga de trabajo                                                       |

| ${\cal D}$                          | Secuencia de puntos dominantes de la curva ${\mathcal C}$                          |

| $\mathcal{E}^u,\mathcal{E}^l$       | Secuencia de puntos asociadas a la envolvente superior e inferior a ${\mathcal C}$ |

| $\mathcal{E}^u_f,\mathcal{E}^l_f$   | Curva digital que determina la envolvente superior e inferior a ${\mathcal C}$     |

| $\mathcal{G}_i$                     | Conjunto de entradas de $g$ pertenecientes a la partición i-ésima                  |

| g                                   | Vector de guarda                                                                   |

| IARD                                | Irregular Access Region Descriptor de un vector de indirección                     |

| L                                   | Tamaño de partición de $a$                                                         |

| l                                   | Vector de accesos mínimos en una clasificación por slices                          |

| $\mathcal{L}\mathcal{I}\mathcal{M}$ | Conjunto de particionamiento de $a$                                                |

| $lim_i^{inf},  lim_i^{sup}$         | Límite inferior y superior asociados a la i-ésima partición de $\boldsymbol{a}$    |

| $N_a$                               | Número de entradas del vector $a$                                                  |

| $N_{\mathcal{C}}$                   | Número de elementos de la curva $\mathcal C$                                       |

| $N_{\mathcal{D}}$                   | Número de elementos del conjunto $\mathcal{D}$                                     |

| $N_{\mathcal{E}}$                   | Número de elementos de los conjuntos $\mathcal{E}^u$ y $\mathcal{E}^l$             |

| $N_p$                               | Número de procesadores                                                             |

| $N_{pt}$                            | Número total de particiones de $a$                                                 |

| $N_S$                               | Número de slices                                                                   |

| $N_{\mathcal{SL}}$                  | Número de secciones lineales                                                       |

|                                     |                                                                                    |

2 Notación

| Símbolo                    | Significado                                                                          |

|----------------------------|--------------------------------------------------------------------------------------|

| $N_{stmt}$                 | Número de estamentos de un lazo irregular                                            |

| $N_x$                      | Número de entradas del vector de indirección $\boldsymbol{x}$                        |

| $p^{max}$                  | Punto de mayor ordenada de un segmento de ${\mathcal C}$                             |

| row                        | Vector de índice de filas de una matriz dispersa                                     |

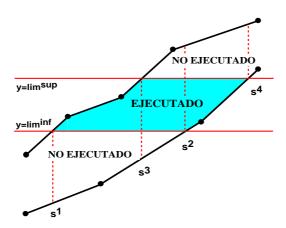

| $\{s^1, s^2, s^3, s^4\}_i$ | Conjunto de índices de $slices$ asociados a la partición i-ésima de $a$              |

| $S_k$                      | Conjunto de entradas del vector de indirección del $slice$ número $k$                |

| $\mathcal{SL}$             | Sección lineal del patrón de acceso                                                  |

| $STMT^k$                   | k-ésima familia de estamentos de un lazo irregular                                   |

| stmt                       | Estamento de un lazo irregular                                                       |

| ticket                     | Ticket table                                                                         |

| $TT_i$                     | Tabla de tangencia asociada al segmento i-ésimo de $\mathcal C$                      |

| u                          | Vector de accesos máximos en una clasificación por slices                            |

| val                        | Vector de valores de una matriz dispersa                                             |

| W                          | Coste del lazo sintético                                                             |

| x                          | Vector de indirección                                                                |

| $x^{fin}$                  | Vector de indirección reordenado                                                     |

| $\mathcal{X}_{s^a}^{s^b}$  | Conjunto de entradas del $x$ comprendidas entre los $slices\ s^a$ y $s^b$            |

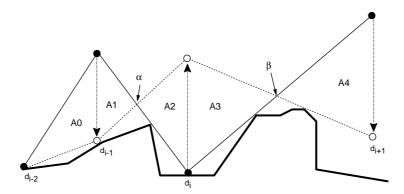

| $\alpha, \beta, \gamma$    | Coste computacional asociado a cada región del patrón de acceso                      |

| $\kappa$                   | Densidad de entradas de $\boldsymbol{x}$ entorno al límite superior de una partición |

| $\lambda$                  | Anchura media de la banda del patrón de acceso                                       |

| $v_p$                      | Potencia de cálculo del procesador $p$                                               |

| ho                         | Vector densidad de una clasificación por slices                                      |

| $ ho_{ini}$                | Vector densidad acumulada                                                            |

### Prefacio

Los sistemas de computación actuales presentan una capacidad de explotación del paralelismo cada vez mayor. Podemos encontrar en el mercado una amplia gama de arquitecturas paralelas que ofrecen una solución competitiva a las demandas de computación existentes. Este paralelismo se explota en todos los niveles que conforman la arquitectura de un computador. Así pues, si consideramos las nuevas tecnologías de diseño de microprocesadores, existe una tendencia a integrar en un mismo circuito un número cada vez mayor de unidades de procesamiento. Si consideramos la organización interna de un computador también existe una tendencia a aumentar el número de procesadores. Si consideramos conjuntos de ordenadores interconectados a través de una red, vemos que también la computación distribuida está siendo objeto de intensos trabajos de investigación.

Debido a que la inmensa mayoría del software existente ha sido diseñado para sistemas con un único procesador, surge la necesidad de adaptar su funcionamiento a un entorno de ejecución paralela. Este proceso resulta extremadamente costoso y en la actualidad se realiza tanto de forma manual, como a través de herramientas de paralelización automática cuya eficiencia es todavía limitada. Los avances conseguidos en este campo se producen a una velocidad menor que la introducción de nuevas tecnologías paralelas. Dicho con otras palabras, cada vez tenemos una cantidad creciente de recursos que explotar y una mayor dificultad para hacerlo. Por este motivo cada vez resulta más crítico la introducción de nuevas propuestas que permitan explotar más eficientemente el paralelismo de los programas.

Por otra parte, la introducción de nuevos procesos de fabricación de circuitos integrados hace que la velocidad de cálculo de los procesadores aumente a un ritmo superior a la velocidad de acceso a memoria. Esto origina un paulatino desequilibrio entre ambos factores que hace que en la actualidad la latencia en los accesos a memoria suponga uno de los principales cuellos de botella en el rendimiento de un computador. Así pues, también es necesario el desarrollo de técnicas que permitan minimizar este efecto, explotando de forma eficiente los niveles inferiores de la jerarquía de memoria del sistema.

4 Prefacio

Un número significativo de aplicaciones reales contiene estructuras de código irregular. Los códigos irregulares se caracterizan por tener un mal comportamiento en los dos tópicos que hemos comentado anteriormente. Por una parte presentan una gran dificultad de análisis, lo que impide extraer el paralelismo de una forma eficiente. Por otra, estos códigos muestran en un gran número de casos una incorrecta explotación de la jerarquía de memoria, lo que limita su eficiencia.

La temática general en la que se enmarca esta tesis es el desarrollo de nuevas estrategias que permitan aumentar el rendimiento en la ejecución de códigos irregulares. Hemos particularizado nuestro estudio a sistemas multiprocesadores, donde es necesario hacer un especial hincapié en los dos factores que determinan de forma más importante la eficiencia de un programa: la extracción eficiente del paralelismo y la explotación, también eficiente, de la jerarquía de memoria. Debido a la estructura de esta clase de códigos, parte del proceso de análisis debe ser realizado durante la ejecución del programa. Por este motivo, un factor adicional que es necesario considerar lo supone el diseño de nuevas rutinas de análisis que minimicen su impacto sobre la ejecución del programa.

Las principales contribuciones realizadas en esta tesis son las siguientes:

- El desarrollo de una estrategia que permite caracterizar el conjunto de accesos a memoria realizados por un código irregular. Esta caracterización es posteriormente utilizada por distintas técnicas de optimización, permitiendo reducir su coste computacional.

- Una nueva técnica de análisis de dependencias con la que podemos determinar la no existencia de conflictos de acceso a memoria de dos códigos irregulares.

- Un conjunto de técnicas de reestructuración tanto del código irregular como de los datos asociados. Estas técnicas están destinadas a extraer el paralelismo y explotar la jerarquía de memoria del sistema.

- Un esquema de organización de las distintas propuestas en un árbol de decisión que permite determinar la solución más eficiente en función de las características del código considerado.

Los distintos trabajos elaborados en el marco de esta tesis han contribuido al desarrollo de las siguientes publicaciones: [96, 97, 127, 128, 129, 130, 131, 132, 133].

### Capítulo 1

### Introducción

Desde el desarrollo del primer ordenador digital programable, de forma pareja al aumento del poder de cálculo y complejidad de estos sistemas, se han incrementado los requisitos computacionales de las aplicaciones ejecutadas en los mismos. Dichos requisitos se deben a dos factores: la carga computacional del programa (evaluada en número de instrucciones) y la cantidad de memoria requerida (evaluada en número de bits). A lo largo de los años, se han desarrollado técnicas de programación cada vez más complejas que demandan una mayor cantidad de recursos. Dentro de este contexto destacamos el desarrollo de mecanismos de acceso a memoria más eficientes, como es el caso del acceso a estructuras de datos irregulares.

Un código irregular se caracteriza por emplear una estructura de acceso compleja con la cual, en muchas situaciones, se logra un aumento del rendimiento del programa mediante una reducción del volumen de datos almacenados. En la actualidad no existe uniformidad de criterios para calificar a una aplicación como irregular. En términos generales, existen dos vertientes distintas para realizar esta clasificación. La primera de ellas se basa en las características del conjunto de posiciones de memoria accedidas a lo largo de la ejecución del programa. De este modo, una aplicación irregular (como contrapartida a una regular) accede a posiciones de memoria no estructuradas que pueden variar dinámicamente durante la ejecución del programa. En la segunda vertiente, el criterio de clasificación está basado en el tipo de mecanismo de indireccionamiento a memoria empleado. Se dice que una aplicación es irregular si contiene estructuras de indireccionamiento que impiden determinar, en tiempo de compilación, el conjunto de accesos a memoria realizados por la aplicación. Ejemplos de estos accesos son los punteros, los vectores de indirección cuyo contenido es desconocido en tiempo de compilación, o el uso de funciones externas

empleadas para direccionar la memoria y cuya estructura tampoco puede ser determinada.

En la actualidad, una gran número de aplicaciones hacen uso de estructuras de almacenamiento irregular. En este sentido, y situándonos en el contexto de la computación de alto rendimiento, resulta necesario que estas aplicaciones sean capaces de explotar, con la mayor eficiencia posible, la arquitectura concreta del sistema en el que son ejecutadas. Usualmente, las aplicaciones se han desarrollado y se siguen desarrollando como programas secuenciales, que son posteriormente modificados y adaptados para permitir su ejecución en un sistema multiprocesador. Desafortunadamente, la amplia variedad de arquitecturas y modelos de paralelización existentes hace necesario que este proceso se realice de forma específica para cada sistema. En muchos casos este proceso se debe realizar manualmente, acarreando importantes costes materiales que pueden hacer inviable el proceso de reestructuración del programa. Con el fin de reducir estos costes se han desarrollado herramientas de paralelización automática que permiten automatizar de forma parcial, o total, este proceso. El funcionamiento de estas herramientas se basa en la identificación y caracterización de las distintas partes de código que comprenden el programa y en la realización de un correcto análisis de dependencias. Para poder realizar dicho análisis es necesario conocer el conjunto de posiciones de memoria accedidas a lo largo de la ejecución del programa. En el caso de los códigos regulares, los accesos a memoria están especificados en la mayor parte de los casos mediante expresiones simples y fácilmente analizables, permitiendo realizar este proceso en tiempo de compilación. Este hecho permite alcanzar una elevada precisión en el análisis de dependencias facilitando el desarrollo de soluciones eficientes para realizar su paralelización de forma automática.

En el caso de los códigos irregulares, los mecanismos de acceso empleados tienen una elevada complejidad y son desconocidos en tiempo de compilación, haciendo que el análisis de dependencias no pueda ser realizado en esta etapa. Ese hecho dificulta enormemente el proceso de paralelización automática, y hace que las herramientas actuales no puedan ofrecer una solución eficiente para la mayor parte de los casos. Otro factor que limita de manera importante el proceso de extracción de paralelismo de un código irregular es la amplia variedad de estructuras existentes. Dado que su definición sólo hace referencia al modo de direccionamiento de los datos, pueden existir códigos irregulares con distinto número de indirecciones, con distintos tipos de dependencias y con mecanismos de acceso diferentes. Cada uno de los cuales necesita un tratamiento específico por parte de la herramienta de análisis, lo que hace que en muchos de los casos, su paralelización quede inabordada. Las estructuras de código irregular suelen aparecer con frecuencia en las regiones más críticas del programa. Debido a este hecho, desde el punto de vista de su adecuación a sistemas multiprocesador se ha originado la necesidad de abordar la paralelización automática de

este tipo de códigos.

Es en este punto donde situamos el contexto en el cual se inició esta tesis. El objetivo propuesto consiste en la optimización de códigos irregulares en el marco de la computación de alto rendimiento. Entendemos por "optimización" al conjunto de procesos que permiten aumentar la eficiencia del programa. Ejemplos de estos procesos son la reestructuración del código secuencial, la mejora en la localidad o la paralelización del programa. En este contexto hemos considerado necesario introducir nuevas propuestas para el análisis y caracterización de códigos irregulares que permitan realizar el proceso de optimización del modo más eficiente. El fin último de nuestro trabajo es la integración de las distintas propuestas en una herramienta de paralelización automática.

En las siguientes secciones describiremos de forma más detallada cada uno de los distintos tópicos que hemos perfilado hasta este momento. Comenzaremos introduciendo las diferentes arquitecturas existentes y los distintos modelos de programación paralela. A continuación definiremos de forma más precisa el tipo de código irregular que hemos considerado, así como sus principales características. Finalmente, mostraremos un esquema general de las contribuciones realizadas en esta tesis.

#### 1.1 Arquitecturas paralelas

Partiendo de la evolución histórica en la arquitectura de los sistemas paralelos, podemos considerar una clasificación en cuatro grandes categorías:

- Multiprocesadores vectoriales.

- Sistemas de memoria distribuida.

- Sistemas de memoria compartida.

- Sistemas altamente distribuidos.

Las arquitecturas vectoriales disponen de unidades aritméticas altamente segmentadas orientas al procesamiento de grandes matrices de datos. Un ejemplo clásico de sistema multiprocesador basado en esta arquitectura fue el Cray X-MP de Cray Research, el cual inició una larga familia de sistemas vectoriales paralelos que finalizó con las series T-90 de Cray. Para conseguir una alta eficiencia, estos sistemas requieren que el código disponga de un basto número de operaciones libres de dependencias. Dichas operaciones deben mostrar una alta regularidad, tanto en su indireccionamiento en memoria como en el tipo

de operación aritmética realizada. Sólo en estos casos el código puede ser eficientemente ejecutado de forma segmentada y paralela. Esta restricción impone una importante limitación en el empleo de este tipo de sistemas, haciendo que su uso resulte eficiente para un conjunto limitado de aplicaciones. A pesar de haber perdido popularidad, hoy en día podemos encontrar en el mercado diferentes sistemas basados en esta arquitectura. Ejemplo de los mismos son las series VPP de Fujitsu, las Series S802 de Hitachi y las series SX de NEC.

Un sistema de memoria distribuida consiste en un conjunto de nodos unidos por una red de interconexión. Cada nodo consta de una memoria local y de uno o varios procesadores. Cada procesador puede acceder a su memoria local, mientras que el único modo de acceso a una memoria remota es mediante el envío de mensajes a través de la red de interconexión. Existen distintas topologías de redes de interconexión, algunas de las cuales pueden alcanzar una alta escalabilidad, permitiendo el desarrollo de sistemas con un ingente número de nodos. Como contraposición, es necesario pagar el precio de una alta latencia en los accesos a posiciones de memoria remotas, lo cual supone el principal factor limitante del rendimiento de estos sistemas. Existen en el mercado un gran número de modelos basados en esta arquitectura. Como ejemplos más representativos podemos citar el sistema T3D de Cray Research, los Connection Machines CM-5 y CM-5E de Thinking Machines Corporation, el SP-2 de IBM y el Sandia de Intel.

En la tercera categoría de nuestra clasificación se sitúan los sistemas de memoria compartida. Estos sistemas constan de una serie de procesadores y bancos de memoria unidos por una red de interconexión. La principal característica de esta clase de sistemas radica en la incorporación de mecanismos (típicamente gestionados por el sistema operativo) que permiten que cada procesador pueda acceder al espacio global de memoria sin la comunicación explícita de mensajes. Dependiendo de la topología concreta de la red de conexión distinguimos, dentro de esta categoría, dos tipos de arquitecturas: la UMA (Uniform Memory Access) y la NUMA (Non-Uniform Memory Access). En la primera de ellas la latencia de acceso a memoria tiene un valor constante que no depende ni del procesador que realiza el acceso ni del banco de memoria accedido. Los sistemas UMA suelen estar organizados mediante un bus de interconexión que conecta los procesadores y los bancos de memoria. Esta estructura se caracteriza por su relativa simplicidad frente a otros esquemas de conexión más complejos. El principal inconveniente de este tipo de arquitecturas es su baja escalabilidad, debido a lo cual sólo alcanza una buena eficiencia con un reducido número de procesadores. Ejemplos de estos sistemas son el Power Challenge de Silicon Graphics, los Y-MP y C90 de Cray y las familias HPC4500 de SUN. En una arquitectura UMA el esquema de distribución de los datos no tiene un impacto significativo

en el rendimiento del sistema. Considerando la jerarquía de memoria de las arquitecturas actuales, el coste de acceso a memoria cache es significativamente inferior al de memoria principal. Por este motivo, la obtención de una alta localidad en los accesos a nivel de memoria cache supone un factor crítico en el rendimiento de esta clase de sistemas.

La segunda gran familia de sistemas de memoria compartida son las arquitecturas NUMA. Estas emplean redes de interconexión con topologías más complejas, en las que tanto los procesadores como los bancos de memoria están distribuidos. La memoria global del sistema, a pesar de poder ser accedida por cualquier procesador, presenta una latencia variable que depende de la posición relativa al procesador que realiza el acceso. Una manera de reducir la latencia y aumentar la escalabilidad consiste en la distribución de los bancos de memoria en nodos siguiendo una estructura similar a los sistemas de memoria distribuida no compartida. De este modo, la red de interconexión une distintos nodos los cuales constan de uno o varios procesadores y una porción de la memoria física global del sistema.

La principal característica de una arquitectura NUMA es la incorporación de mecanismos hardware para gestionar los accesos a memoria remota y para mantener la coherencia de la información del mismo modo que sucede en las arquitecturas UMA. Algunos sistemas, denominados Cache-Coherent NUMA (CC-NUMA), mantienen la coherencia en todos los niveles de la jerarquía de memoria. En este tipo de sistemas, la obtención de una alta localidad en los accesos tiene una gran influencia en su rendimiento. A diferencia de las arquitecturas UMA, donde sólo es necesario explotar la memoria cache, en un sistema NUMA también es importante maximizar la localidad en los accesos a memoria principal. Como ejemplos de arquitecturas NUMA podemos citar la familia Origin de Silicon Graphics, el T3E de Cray y el HP Exemplar. En la actualidad el uso de estas arquitecturas está muy diversificado y gozan de una gran popularidad debido a que obtienen un correcto equilibro entre escalabilidad y facilidad de programación.

Una última categoría de nuestro esquema de clasificación lo compone los sistemas altamente distribuidos. En esta clase de sistemas se prima la modularidad de cada elemento a costa de unas prestaciones inferiores en la red de interconexión. Recientemente, el empleo de esta clase de sistemas está experimentando un auge y su diseño y optimización está siendo objeto de intensos estudios de investigación. Los aspectos claves de este tipo de arquitectura son el establecimiento de un proceso de control del sistema distribuido. Control que debe realizar una distribución eficiente de las computaciones en función de las características potencialmente heterogéneas de esta arquitectura.

El tipo de sistema paralelo ejerce un papel determinante en los mecanismos de optimización utilizados. Nuestras propuestas están enmarcadas en el empleo de sistemas paralelos de memoria compartida. Existen distintos motivos para realizar esta elección: el primero de ellos es que debido a su amplia difusión y popularidad, entendemos que las aportaciones realizadas en esta tesis suponen un mayor beneficio a la comunidad científica. El segundo motivo es la disponibilidad de herramientas de paralelización automática orientadas a esta arquitectura en las que nuestras propuestas pueden ser integradas. Un último motivo que hemos encontrado para el empleo de esta clase de sistemas es su disponibilidad, tanto en el propio departamento, como en otros centros de supercomputación a los que tenemos acceso.

#### 1.2 Modelos de programación paralela

En la actualidad existen tres modelos ampliamente difundidos de programación paralela,

- Modelo de programación por pase de mensajes.

- Modelo de programación Data Parallel.

- Modelo de programación sobre memoria compartida.

El modelo de programación por pase de mensajes fue introducido para la paralelización de programas en sistemas distribuidos. En la actualidad, este modelo tiene un uso extendido en un gran número de plataformas, siendo también soportado por la mayor parte de las arquitecturas de memoria compartida. Este modelo de programación se basa en la comunicación de los procesadores implicados en la ejecución del programa mediante el envío y la recepción de mensajes. Típicamente, el esquema de programación utilizado es el de Simple Programa Múltiple Dato (SPMD) en el que se deben establecer de forma explícita los distintos tipos de operaciones de comunicación y sincronización entre los procesadores, así como la distribución de los datos. Estas operaciones suelen estar contenidas en una librería de rutinas de comunicación. Como ejemplos de estas librerías podemos citar la Parallel Virtual Machine [46] (PVM), la cual fue la primera librería en ser ampliamente utilizada. Posteriormente se ha introducido la Message Passing Interface [48] (MPI), la cual se ha establecido como un estándar de comunicación por pase de mensajes. Otros ejemplos son las primitivas put y get [102] empleadas en sistemas de memoria compartida. La programación mediante este modelo se realiza de forma manual, en función de

las características del programa y del tipo de arquitectura utilizada. Este hecho resta versatilidad y flexibilidad a esta propuesta, introduciendo una importante limitación para su empleo.

El modelo de programación Data Parallel supera esta limitación haciendo que los procesos de comunicación y sincronización sean transparentes al usuario. De esta forma, el programador únicamente debe establecer la distribución de los datos sobre un espacio de memoria que se muestra como global. Posteriormente, en la etapa de compilación se genera de forma automática el programa SPMD específico para cada arquitectura. Dicho programa contiene todas las rutinas de comunicación y sincronización necesarias para llevar a cabo la distribución de los datos y la ejecución del programa paralelo. Ejemplos de modelos data-parallel son el Fortran-D [66], el Vienna Fortran [25] y el High Performance Fortran [82] (HPF). Este último modelo goza de una gran difusión, pudiéndose utilizar en la práctica totalidad de las plataformas existentes. A pesar de ello, en los últimos años han surgido críticas por la limitada eficiencia de su empleo en la paralelización de programas.

Los modelos de programación sobre sistemas de memoria compartida se basan en el uso de directivas de paralelización mediante las cuales se realizan las operaciones de distribución de los datos y de sincronización entre los procesadores. Dado que un sistema de memoria compartida facilita que cada procesador tenga acceso al espacio global de memoria, desaparece la necesidad de comunicar explícitamente los datos. Mediante este modelo, además de permitir realizar la distribución de los diferentes datos, se puede determinar la granularidad del paralelismo utilizado (iteraciones de un lazo, secciones de código, etc.) y especificar la carga de trabajo asignada a cada procesador. La programación se realiza, tanto a través de directivas de alto nivel que especifican el grado de paralelismo del programa, como de operaciones de sincronización de bajo nivel que determinan un orden adecuado de ejecución y de acceso a los datos. Inicialmente, se establecieron dos modelos de programación ampliamente difundidos: el Parallel Computing Forum [43] (PCF) y OpenMP [24]. Adicionalmente, existía un variado número de librerías de memoria compartida asociadas a cada sistema particular. Ejemplos de las mismas son el SUNMP [112] y las directivas MP de Silicon Graphics [92]. Estas librerías ofrecían un conjunto de directivas específicas a la arquitectura del sistema particular, las cuales permitían generar, en dichas arquitectura, una versión paralela que por lo general era eficiente. El inconveniente de estas directivas específicas era la pérdida de portabilidad en el programa paralelo. En la actualidad, el OpenMP se ha convertido en el modelo de programación estándar de sistemas de memoria compartida. Su uso está ampliamente difundido, y es el modelo adoptado por la mayor parte de los compiladores.

OpenMP es una especificación destinada a expresar el paralelismo en sistemas de memoria compartida mediante implementación portable para Fortran, C y C++. El OpenMP ofrece un conjunto de directivas de compilación que permiten establecer regiones paralelas en el programa, realizar distintos tipos de sincronizaciones, y dar soporte para la compartición o privatización de los datos. Adicionalmente, contiene una librería de rutinas que permiten controlar el entorno de ejecución del programa y dan soporte para la realización accesos atómicos a posiciones de memoria. Finalmente, este modelo de programación permite especificar, mediante variables de entorno, ciertos parámetros asociados a la ejecución paralela.

En el trabajo desarrollado en esta tesis hemos adoptado el modelo de programación sobre memoria compartida, dado que es la opción más adecuada para el tipo de arquitectura utilizada. Más concretamente, y debido a su amplia difusión y versatilidad, hemos empleado OpenMP sobre programas escritos en Fortran 77. La elección de este lenguaje de programación se debe a dos motivos. Por una parte el Fortran 77 es el lenguaje de programación utilizado por la mayor parte de los códigos de pruebas que hemos considerado. Esto se debe a que es el lenguaje de programación más utilizado en aplicaciones en las que prima el carácter computacional. El segundo motivo radica en que también es el lenguaje empleado por otros autores para implementar sus técnicas de optimización, lo cual nos va a facilitar la realización de comparativas con las propuestas que nosotros vamos a realizar.

# 1.3 Herramientas de paralelización automática

Actualmente existen distintas herramientas destinadas a realizar de forma automática la optimización y paralelización de programas. Ejemplo de dichas herramientas son los compiladores académicos Polaris, SUIF y PIPS, y el compilador comercial MIPSpro. En esta sección describimos sus principales características.

Comenzaremos nuestra descripción con el compilador **Polaris** [18], desarrollado en la Universidad de Illinois. Esta herramienta utiliza como entrada un código escrito en Fortran 77 que convierte, después de realizar distintos procesos de análisis y optimización [41], en un código paralelo orientado a una arquitectura específica. En la actualidad, este compilador genera códigos para arquitecturas de memoria compartida UMA como el Power Challenge de Silicon Graphics o el Convex C3, arquitecturas de memoria compartida NUMA como la familia Origin de Silicon Graphics o el Cray T3E y arquitecturas de memoria distribuida como el Cray T3D.

Las principales características de este compilador son su capacidad de realizar un

análisis simbólico del programa, mediante el cual puede identificar operaciones de reducción tanto escalares como de histograma, caracterizar las variables de inducción obteniendo su expresión analítica, llevar a cabo la eliminación de código muerto, aplicar técnicas de in-linning, privatizar variables [139], etc. Además, incorpora distintos mecanismos de análisis de dependencias que pueden ser extendidos a un análisis interprocedural [117]. Adicionalmente, esta herramienta permite introducir en el programa de entrada una serie de directivas para indicar, de forma explícita, el grado de paralelismo de diferentes partes del programa. Una importante característica de Polaris es que permite acceso a su representación interna [41], lo cual sirve de infraestructura para implementar y evaluar nuevas técnicas de análisis y optimización de códigos.

El rendimiento de esta herramienta ha sido evaluado de forma exhaustiva empleando conjuntos de programas de prueba como el *Perfect Benchmark* y el SPEC95fp [38]. Los resultados obtenidos muestran su eficiencia cuando se aplica sobre códigos regulares. En el caso de los códigos irregulares, la eficiencia de Polaris es más limitada, restringiéndose a la identificación y paralelización de operaciones de reducción. Esta última operación se lleva a cabo mediante la técnica de *array expansion* [42, 38]. En este sentido, uno de los desafíos existentes en la actualidad es la incorporación de nuevas propuestas en este campo.

El compilador SUIF [55] (Stanford University Intermediate Format2), desarrollado en la Universidad de Stanford, ofrece una plataforma para la investigación y de desarrollo de nuevas técnicas de optimización de programas. En su diseño se ha primado la facilidad de empleo y la capacidad de modificar y ampliar su contenido de un modo simple. Esta herramienta es capaz de analizar programas escritos en lenguaje C o Fortran, devolviendo, en ambos casos, un código paralelo SPMD expresado en lenguaje C.

Esta herramienta incluye técnicas de análisis de dependencias y análisis simbólico, permitiendo extraer paralelismo en el código y mejorar la localidad tanto del programa secuencial como del paralelo. Una de sus principales bazas es su importante mecanismo de análisis interprocedural. La herramienta SUIF incorpora distintas técnicas para identificar y paralelizar operaciones de reducción, tanto regulares como irregulares. En este último caso emplea, como método de paralelización, la técnica de replicated buffers [145], la cual se describirá posteriormente. SUIF permite la portabilidad del código paralelo generado a plataformas de memoria compartida de Silicon Graphics, el sistema multiprocesador DASH de Stanford [89] y el Kendall Square Research KSR1.