#### PhD Thesis

# Parallel Prefix Operations on Heterogeneous Platforms

Adrián Pérez Diéguez 2018

# Parallel Prefix Operations on Heterogeneous Platforms

Adrián Pérez Diéguez

PhD Thesis

October 2018

PhD Advisors:

Margarita Amor López Ramón Doallo Biempica

PhD Program in Information Technology Research

Dra. Margarita Amor López Profesora Titular de Universidade Dpto. de Enxeñaría de Computadores Universidade da Coruña Dr. Ramón Doallo Biempica Catedrático de Universidade Dpto. de Enxeñaría de Computadores Universidade da Coruña

#### **CERTIFICAN**

Que a memoria titulada "Parallel Prefix Operations on Heterogeneous Platforms" foi realizada por D. Adrián Pérez Diéguez baixo a nosa dirección no Departamento de Enxeñaría de Computadores da Universidade da Coruña, e conclúe a Tese de Doutoramento que presenta para a obtención do título de Doutor en Enxeñaría Informática pola Universidade de Coruña coa Mención de Doutor Internacional.

En A Coruña, a de de 2018

Asdo.: Margarita Amor López Asdo.: Ramón Doallo Biempica

Directora da Tese de Doutoramento Director da Tese de Doutoramento

Asdo.: Adrián Pérez Diéguez Autor da Tese de Doutoramento

Aos que me apoiastes nesta andaina, mais sobre todo aos meus pais.

## Agradecementos

En primeiro lugar, quixera agradecerlle aos meus directores, Marga e Ramón, a oportunidade que me deron ao confiar en mín, a súa dedicación e prezada axuda, pero especialmente a paciencia acadada conmigo. Foi unha honra ter traballado ao voso lado todos estes anos, unha etapa da miña vida que non esquecerei endexamais. Aínda que tamén me gustaría estender este recoñecemento a todos os profesores do Grupo de Arquitectura de Computadores.

Tamén quixera mostrar o meu agradecemento, dun xeito especial, aos meus compañeiros de laboratorio, aos que seguen nel e aos que xa marcharon. Unha relación que sen dúbida vai moito máis alá do académico, e que agardo que se manteña por moitos anos. Foi unha ledicia compartir todos eses momentos con vós. En particular, sería inxusto non destacar a labor de Jacobo nesta tese, o meu mentor e salvador asemade nos primeiros pasos desta aventura.

Pero se alguén debe ser nomeado, eses son os meus pais. Sacrificaron todo para darme a oportunidade de estar eu aquí. Non teño palabras para vós, moitas grazas de corazón. Tamén ao meu irmán e a toda a miña familia. Aos meus compañeiros de piso destes anos, aos meus amigos de Pontevedra, de Coruña e aos que están espallados por ahí adiante, aos que fixen no mundo do deporte, da cultura e das reivindicacións, non me esquezo de vós. A todos eles, envíolles hoxe unha aperta.

Of course, I do not want to forget the japanese people. I gratefully thank Dr. Satoshi Matsuoka and Dr. Akira Nukada for hosting and advising me during my visit to the Tokyo Institute of Technology, Japan, and also the Titech people, but especially Sergio, Shweta, Kevin, Pak, Xu and Artur. *Arigato gozaimasu*.

Finalmente, gustaríame estender o meu agradecemento a todas as entidades que financiaron este traballo. Dunha parte, ás redes estatais de investigación CAPAP-H4 e CAPAP-H5, ás redes europeas NESUS IC1305 e HiPEAC, á Xunta de Galicia (ref. GRC2013/055, ED431C 2017/04, R2014/041, ED431D R2016/05, ED431G/01 e a axuda predoutoral ED481A-2015/230) e ao Goberno de España (ref. TIN2013-42148-P, TIN2016-75845-P, axuda predoutoral FPU14/02801 e de estadía EST16/00579). Así mesmo, ao Grupo de Arquitectura de Computadores, ao Departamento de Enxeñaría de Computadores e á Universidade da Coruña. Tamén, á empresa Inditex polo financiamento dunha estadía.

Adrián Pérez Diéguez

Nothing has such power to broaden the mind as the ability to investigate systematically and truly all that comes under thy observation in life.

(Nada ten tanto poder para ampliar a mente coma a capacidade de investigar de xeito sistemático e real todo o que é susceptible de observación na vida)

Marco Aurelio

## Resumo

As tarxetas gráficas, coñecidas como GPUs, aportan grandes vantaxes no rendemento computacional e na eficiencia enerxética, sendo un piar clave para a computación de altas prestacións (HPC). Sen embargo, esta tecnoloxía tamén é custosa de programar, e ten certos problemas asociados á portabilidade entre as diferentes tarxetas. Por outra banda, os algoritmos de prefixo paralelo son un conxunto de algoritmos paralelos regulares e moi empregados nas ciencias compuacionais, cuxa eficiencia é esencial en moitas aplicacións. Neste eido, aínda que as GPUs poden acelerar a computación destes algoritmos, tamén poden ser unha limitación cando non explotan axeitadamente o paralelismo da arquitectura GPU.

Esta Tese presenta dúas perspectivas. Dunha parte, deséñanse novos algoritmos de prefixo paralelo para calquera paradigma de programación paralela. Pola outra banda, tamén se propón unha metodoloxía xeral que implementa eficientemente algoritmos de prefixo paralelos, de xeito doado e portable, sobre arquitecturas GPU CUDA, mais que se centrar nun algoritmo particular ou nun modelo concreto de tarxeta. Para isto, a metodoloxía identifica os paramétros da GPU que inflúen no rendemento e, despois, seguindo unha serie de premisas teóricas, obtéñense os valores óptimos destes parámetros dependendo do algoritmo, do tamaño do problema e da arquitectura GPU empregada. Ademais, esta Tese tamén prové unha serie de funcións GPU compostas de bloques de código CUDA modulares e reutilizables, o que permite a implementación de calquera algoritmo de xeito sinxelo. Segundo o tamaño do problema, propóñense tres aproximacións. As dúas primeiras resolven problemas pequenos, medios e grandes nunha única GPU, mentras que a terceira trata con tamaños extremadamente grandes, usando varias GPUs.

As nosas propostas proporcionan uns resultados moi competitivos a nivel de rendemento, mellorando as propostas existentes na bibliografía para as operacións probadas: a primitiva *scan*, ordenación e a resolución de sistemas tridiagonais.

## Resumen

Las tarjetas gráficas (GPUs) han demostrado grandes ventajas en el rendimiento computacional y en la eficiencia energética, siendo una tecnología clave para la computación de altas prestaciones (HPC). Sin embargo, esta tecnología también es costosa de programar, y tiene ciertos problemas asociados a la portabilidad de sus códigos entre diferentes generaciones de tarjetas. Por otra parte, los algoritmos de prefijo paralelo son un conjunto de algoritmos regulares y muy utilizados en las ciencias computacionales, cuya eficiencia es crucial en muchas aplicaciones. Aunque las GPUs puedan acelerar la computación de estos algoritmos, también pueden ser una limitación si no explotan correctamente el paralelismo de la arquitectura GPU.

Esta Tesis presenta dos perspectivas. De un lado, se han diseñado nuevos algoritmos de prefijo paralelo que pueden ser implementados en cualquier paradigma de programación paralela. Por otra parte, se propone una metodología general que implementa eficientemente algoritmos de prefijo paralelo, de forma sencilla y portable, sobre cualquier arquitectura GPU CUDA, sin centrarse en un algoritmo particular o en un modelo de tarjeta. Para ello, la metodología identifica los parámetros GPU que influyen en el rendimiento y, siguiendo un conjunto de premisas teóricas, obtiene los valores óptimos para cada algoritmo, tamaño de problema y arquitectura. Además, las funciones GPU proporcionadas están compuestas de bloques de código CUDA reutilizable y modular, lo que permite la implementación de cualquier algoritmo de prefijo paralelo sencillamente. Dependiendo del tamaño del problema, se proponen tres aproximaciones. Las dos primeras resuelven tamaños pequeños, medios y grandes, utilizando para ello una única GPU; mientras que la tercera aproximación trata con tamaños extremadamente grandes, usando varias GPUs.

Nuestras propuestas proporcionan resultados muy competitivos, mejorando el rendimiento de las propuestas existentes en la bibliografía para las operaciones probadas: la primitiva *scan*, ordenación y la resolución de sistemas tridiagonales.

## Abstract

Graphics Processing Units (GPUs) have shown remarkable advantages in computing performance and energy efficiency, representing one of the most promising trends for the near-future of high performance computing. However, these devices also bring some programming complexities, and many efforts are required to provide portability between different generations. Additionally, parallel prefix algorithms are a set of regular and highly-used parallel algorithms, whose efficiency is crutial in many computer science applications. Although GPUs can accelerate the computation of such algorithms, they can also be a limitation when they do not match correctly to the GPU architecture or do not exploit the GPU parallelism properly.

This dissertation presents two different perspectives. On the one hand, new parallel prefix algorithms have been algorithmically designed for any parallel programming paradigm. On the other hand, a general tuning GPU methodology is proposed to provide an easy and portable mechanism to efficiently implement parallel prefix algorithms on any CUDA GPU architecture, rather than focusing on a particular algorithm or a GPU model. To accomplish this goal, the methodology identifies the GPU parameters which influence on the performance and, following a set of performance premises, obtains the convinient values of these parameters depending on the algorithm, the problem size and the GPU architecture. Additionally, the provided GPU functions are composed of modular and reusable CUDA blocks of code, which allow the easy implementation of any parallel prefix algorithm. Depending on the size of the dataset, three different approaches are proposed. The first two approaches solve small and medium-large datasets on a single GPU; whereas the third approach deals with extremely large datasets on a Multiple-GPU environment.

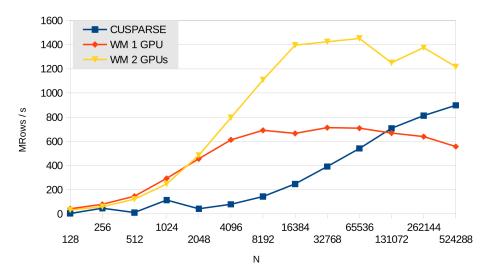

Our proposals provide very competitive performance, outperforming the stateof-the-art for many parallel prefix operations, such as the scan primitive, sorting and solving tridiagonal systems.

## **Preface**

#### Introduction and Motivation

In recent years, GPUs (*Graphics Processing Units*) have experienced a noticeable increase in their relevance and usage in high performance computing, since they can perform much faster than regular CPUs (*Central Processing Units*). Parallel computing is a form of computation in which many calculations are performed simultaneously. Parallel computing involves different perspectives, being this work mainly focused on: computer architecture and parallel programming. Computer architecture (hardware aspect) refers to support parallelism at architectural level, whereas parallel programming (software aspect) focuses on fully using the computational power of the target architecture.

From a computer architecture perspective, modern GPUs can execute up to a thousand of physical threads per device, which are optimized for intensive arithmetic operations, performing especially well in regular algorithms with reduced flow control, and better hiding the execution latencies owing to overlap computation and communication. This overlapping is possible thanks to assign a certain number of logical threads to each core, reducing idle cycles through multi-threading.

From a programmability point of view, the CPU programmability has much more advantages. First, there are many APIs to facilitate the parallel adaptation from a serial code to a parallel approach, such as OpenMP [21], and parallel programming libraries like MPI [47]. Furthermore, there is a huge and experienced community behind the programming languages focused on a CPU, such as C++, Python and Java, providing easy and powerful tools for software development, profiling and debugging on these languages. In contrast, most of the high level GPU

languages are quite recent; thus, specialized developing tools, APIs and libraries are scarce. Additionally, this novel GPU capability is limited by the overall complexity of hardware and typical workloads. Programmers have to choose suitable parallel algorithms for these architectures that also require special languages such as CUDA [93] or OpenCL [68]; and also have to fully understand the hardware and the problem, considering optimization techniques to fully exploit the GPU resources and achieve the said performance.

There are several proposals in order to facilitate the programmability of these architectures: Autotuning [38], directives [131], automatic compilers [2] or accelerated libraries [44]. Autotuning [38] [73] is a very interesting option for applications whose execution time, memory usage or energy consumption can vary depending on a set of parameters and their execution environment. The autotuner determines the best parameter combination to maximise an user-defined metric. Nevertheless, this technique requires writing code in a parametrized way to accommodate various performance tuning parameters. Another approach is the use of directives such as OpenACC [131] or hiCuda [55]. Most of this kind of libraries require to have GPU expertise. Furthermore, the code is not easily readable and there are also some limits, for example, the programmer cannot use CUDA intrinsic functions within the accelerator region. Automatic compilers are another interesting option that automatically generate code for GPUs, such as Par4all [2] and Bones [88], saving time and effort to programmers. However, these approaches sometimes rely on the user knowledge for tuning applications. In addition, some systematic code translations, without a previous analysis of the problem, can lead to reduce performance. Finally, the use of accelerated tuned libraries for each architecture version, such as SkePU [44], MAGMA [64] or SkelCL [118], can enable applications to fully exploit the power of current heterogeneus parallel systems. Due to the fast GPU market evolution, each GPU architecture version highly vary its desing from one generation to another, and the parameters which influence on performance also change and must be re-adjusted.

This Thesis is primarily interested on the forth approach, tuning an *accelerated library*, as it provides an optimal implementation independently of the target architecture, providing generality and usability, and being transparent to the user.

On the one hand, a parallel computation is work efficient when it does not perform more work than its sequential version; in other words, both versions have the same complexity. An approach that is work efficient follows a work and depth based model. On the other hand, a processor based model takes into account computing costs, such as execution times, the number of processors, synchronization barriers or communications costs of the implementation, trying to minimize the execution time of the algorithm, but not the work efficiency. In this work, the complexity of the algorithms is not analyzed; only final execution times are considered, following a processor based model. On the other hand, the complexity of GPU hardware is reflected in the diversity of its performance models, and it is not easy predict how long an implementation takes or suggest a precise formula to find out its optimal GPU parameters. In [62], a very complex model is presented, using more than 20 equations; whereas a model formulation based on graphs was presented in [5]. Additionally, other proposals can be found in [1] and [22].

### Objectives and Work Methodology

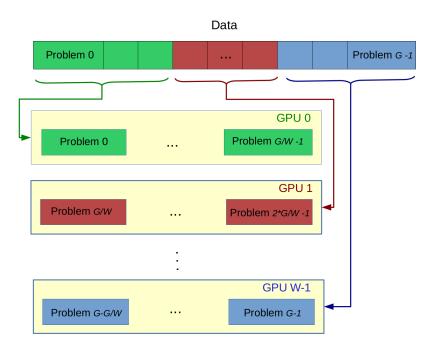

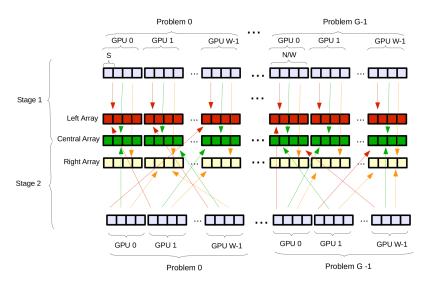

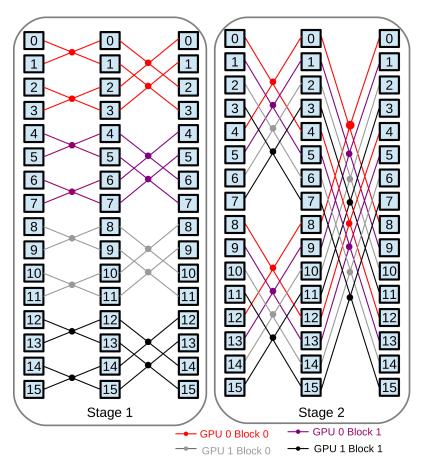

The aim of this Thesis is to propose a GPU performance parameter tuning methodology to predict the best GPU parameter configuration that influences on the performance for each GPU architecture generation, especially focused on a set of regular and highly-used parallel algorithms, called pararell prefix algorithms [75] [76], as well as designing and developing new pararell prefix algorithms that match well to the parallel paradigm. These algorithms are regular algorithms whose communication pattern does not depend on execution values, as it is given by a linear function which is well suited to GPU architectures. Furthermore, each resulting element is a combination of previous results from other elements with common calculations that can be reused. Therefore, using the proposed methodology is posible to efficiently parallelize and solve several frequently used operations: the Fast Fourier Transform (FFT), the scan primitive, tridiagonal system solvers (TS) or sorting. Regarding this methodology, these problems can be classified depending on their size:

■ Small datasets. The problem data fit in the GPU scratchpad memory (also known as shared-memory in CUDA architectures).

- Medium and Large datasets. The problem size is bigger than the scrathpad memory but still fits into the device memory of a single GPU.

- Extremely Large datasets. The problem size is bigger than the device memory of a single GPU, and the dataset is distributed among several GPUs.

To accomplish our goal, this research work has evolved across these three stages, progressively developing an incremental methodology for each kind of dataset and adapted to different CUDA architectures. Firstly, a tuning methodology was proposed for small datasets, providing an efficient implementation for both tridiagonal systems, the scan primitive and a sorting algorithm. After this, we have increased the methodology to support medium and large datasets, implementing different scan and tridiagonal system solver approaches under this methodology. Finally, the methodology was extended to extremely large datasets, introducing several GPUs and computing nodes in the design, providing an efficient proposal for the scan primitive. It should be observed that the scope of this work is limited to CUDA GPUs, as it is the leading programming model and pioneer for general-purpose computing on GPUs, but the proposals of this Thesis could be applied to other frameworks, as OpenCL, as long as similar hardware architecture is used. In addition to the tuning methodology, this Thesis also provides three new parallel prefix algorithms, two for solving tridiagonal systems and one for sorting. These algorithms were designed from a algorithmical perspective to match well to any parallel paradigm, demonstrating their efficiency on GPUs.

In [8], a dissertation about tuning GPU performance parameters for *Index-Digit* algorithms and small datasets is presented. In contrast to that text, this work extends the methodology for *parallel prefix* algorithms, a superset that also includes *Index-Digit* algorithms, as will be explained later, as well as supporting medium, large and extremely large datasets.

#### Main Contributions of the Thesis

The main contributions of this Thesis are the following:

- A literature review about the most employed parallel prefix algorithms and recent Graphic Processing Units (GPUs).

- Design, development and algorithmic formulation of new parallel prefix algorithms.

- Development of a general tuning methodology for parallel prefix algorithms and Index-Digit algorithms on different GPU systems.

- Experimental analysis of the proposed methodology for several parallel prefix operations.

- Provide an accelerated GPU library that outperforms the state-of-the-art for the corresponding operations.

- Thorough performance evaluation of the library using real-world applications.

#### Structure of the Thesis

This Thesis is organized as follows:

- Chapter 1 introduces the Graphcis Processing Units (GPUs) and describes the basics of CUDA programming and its execution model. Additionally, it also summarizes the GPU architectures employed in this Thesis.

- Chapter 2 defines both the parallel prefix algorithms and a subset of them called Index-Digit algorithms. Specifically, the following algorithms are analyzed in this chapter: Tridiagonal system solvers, scan primitive and sorting algorithms.

- Chapter 3 presents the new parallel prefix algorithms designed and developed in this Thesis. These new algorithms are algorithmically formulated in this

chapter, and also a hand-tuned GPU implementation is provided for some of them. Concretely, two new algorithms are created to solve tridiagonal systems, and a new algorithm for sorting is also proposed.

- Chapter 4 addresses the development of a general GPU tuning methodology for both parallel prefix algorithms and Index-Digit algorithms, considering datasets that fit in the shared memory a of CUDA GPU, and providing an accelerated library with the corresponding implementations. The proposed methodology is analyzed against the state-of-the-art, and the experimental results are presented.

- Chapter 5 conducts the extension of the previous methodology to larger datasets which do not fit in the shared memory of a GPU but still can be stored in the device memory of a single GPU. The methodology is also tested for well-known operations, surpassing the state-of-the-art on different GPU architectures.

- Chapter 6 extends the proposed methodology for extremely large datasets which cannot be stored in a single GPU, needing a Multiple-GPU system. The resulting library based on the methodology is tested for tridiagonal systems and the scan primitive in different Multiple-GPU environments, analyzing the experimental results of their execution.

- Chapter 7 analyzes the efficiency of the final library built on this Thesis in real-world applications. Specifically, the multiplication of high-precision integers, which is used in many computer science fields, such as cryptography, is tested using our proposal.

- Chapter 8 extracts the conclusions of the Thesis and presents the future work.

### Funding and Technical Means

The following means and funding have been used to carry out this Thesis:

Working material, as well as human and financial support provided by the Computer Architecture Group (GAC) of the University of A Coruña.

- Fellowships funded by the Ministry of Education, Culture and Sport of Spain (FPU program, ref. FPU14/02801) and by the Galician Government (Xunta de Galicia, ref. ED481A-2015/230).

- Access to bibliographical material through the library of University of A Coruña.

- Additional funding through the following research projects:

- European funding: "Network for Sustainable Ultrascale Computing" (NESUS COST Action ref. IC1305), "High-Performance Embedded Architecture and Compilation Network of Excellence" (HiPEAC3 NoE).

- State funding by the Ministry of Economy and Competitiveness of Spain through the projects "New Challenges in High Performance Computing: from Architectures to Applications" (refs. TIN2013-42148-P and TIN2016-75845-P); and the "Red de Computación de Altas Prestaciones en Arquitecturas Heterogéneas" (CAPAP-H4 and CAPAP-H5).

- Regional funding by the Galician Government (Xunta de Galicia) under the Consolidation Program of Competitive Research Groups (Computer Architecture Group, refs. GRC2013/055 and ED431C 2017/04); Network of Cloud and Big Data Technologies for HPC (refs R2014/041 and ED431D R2016/045) and Funding for the Accreditation, Structuring and Improvement of the Remarkable Research Centre on Information and Communication Technology (CITIC ref. ED431G/01).

- Access to clusters, supercomputers and other computing platforms:

- *Pluton* cluster (Computer Architecture Group, University of A Coruña, Spain).

- Roma and Warsaw cluster (Global Scientific Information and Computing Center, Tokyo Institute of Technology, Japan).

- TSUBAME-KFC supercomputers (Global Scientific Information and Computing Center, Tokyo Institute of Technology, Japan).

- DGX-1 workstation by the Real World Big-Data Computation Open Innovation Laboratory (RWBC-OIL) (National Institute of Advanced Industrial Science and Technology (AIST), Japan and NVIDIA Company)

- NVIDIA Tesla Kepler K40 card donated by NVIDIA Company.

- Two three-month research visits to the Global Scientific Information and Computing Center at Tokyo Institute of Technology in Japan, funded by the Ministry of Education, Culture and Sport of Spain (ref. EST16/00579), by the INDITEX-UDC 2016 collaboration grant and by the High-Performance Embedded Architecture and Compilation Netfowrk of Excellence Collaboration 2017 Grant.

#### Registered Software

The following software product has been registered in the IP registry as outcome of this Thesis:

Adrián Pérez Diéguez, Jacobo Lobeiras Blanco, Margarita Amor López, Ramón Doallo Biempica. BPLG: A Tuned Butterfly Processing Library for GPUs architectures. December 2016. Record entry number: C-241-2016. Owning entity: Universidade da Coruña. Priority country: Spain.

#### Publications from the Thesis

#### Journal Papers (5)

Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Tree Partitioning Reduction: A New Parallel Partition Method for Solving Tridiagonal Systems. In ACM Transactions on Mathematical Software. (Accepted under second revision).

JCR Impact Factor (2017): 2.905, Q1 in Computer Science, Hardware & Architecture.

Adrián P. Diéguez, Margarita Amor, Ramón Doallo, Akira Nukada, Satoshi Matsuoka. Efficient High-Precision Integer Multiplication on the GPU. In International Journal of High Performance Computing Applications. (Submitted)

JCR Impact Factor (2017): 2.015, Q2 in Computer Science, Hardware & Architecture.

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Parallel Prefix Operations on GPU: Tridiagonal System Solvers and Scan Operators. In *The Journal of Supercomputing* (Accepted under second revision).

JCR Impact Factor (2017): 1.532, Q2 in Computer Science, Hardware & Architecture.

- Adrián P. Diéguez, Margarita Amor, Jacobo Lobeiras, Ramón Doallo. Solving Large Problem Sizes of Index-Digit Algorithms on GPU: FFT and Tridiagonal System Solvers. In *IEEE Transactions on Computers*, volume 67, issue 1, pages 86-101. January 2018.

JCR Impact Factor: 3.052, D1/Q1 in Computer Science, Hardware & Architecture.

DOI 10.1109/TC.2017.2723879

Adrián P. Diéguez, Margarita Amor, Ramón Doallo. BPLG-BMCS: GPU-Sorting Algorithm using a Tuning Skeleton Library. In *The Journal of Super-computing*, volume 73, issue 1, pages 4-16. January 2017.

JCR Impact Factor: 1.532, Q2 in Computer Science, Hardware & Architecture.

DOI 10.1007/s11227-015-1591-9

#### International Conferences (7)

Adrián P. Diéguez, Margarita Amor, Ramón Doallo. A Tuning Strategy for Tridiagonal System Solvers on GPU. In 18th International Conference on Computational and Mathematical Methods in Science and Engieering (CMMSE'18). July 2018.

ISBN 978-84-697-7861-6

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo, Akira Nukada, Satoshi Matsuoka. Efficient Solving of Scan Primitive on Multi-GPU Systems. In 32nd IEEE International Parallel and Distributed Processing Symposium (IPDPS'18), pages 794-803. May 2018. ISSN 1530-2075

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Solving Multiple Tridiagonal Systems on a Multi-GPU Platform. In 26th Euromicro International Conference on Parallel, Distruted and Network-based Processing (PDP'18), pages 759-763. March 2018.

ISSN 2377-5750

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. New Tridiagonal System Solver on GPU architectures. In 22th International Conference on High Performance Computing (HiPC'15), pages 85-93. December 2015. ISBN 978-1-46738487-2

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Solving Tridiagonal Systems with BPLG Library. In 11th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES'15), pages 267-270. July 2015.

ISBN 978-88-905806-3-5

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. BS-Comb: An Efficient Sorting Algorithm for GPUs. In 15th International Conference on Computational and Mathematical Methods in Science and Engineering (CMMSE'15), pages 461-473. July 2015. ISBN 978-84-617-2230-3

- Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Efficient Scan Operator Methods on a GPU. In 26th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD'14), pages 190-197. October 2014.

ISSN: 1550-6533

#### Book Chapters (1)

Adrián P. Diéguez, Margarita Amor, Ramón Doallo. Chapter: Techniques for Autotuning Algorithms on Heterogeneous Platforms. In First PhD Symposium on Sustainable Ultrascale Computing Systems, pages 25-28. Computer Architecture, Communications and Systems Group (ARCOS) University Carlos III Madrid. Spain (2016).

ISBN 978-84-608-6309-0

#### National Conferences (1)

Adrián P. Diéguez, Margarita Amor, Ramón Doallo. CUDA Optimization Techniques for Scan Operator. In XXV Jornadas de Paraalelismo, pages 287-292. September 2014.

ISBN: 84-697-0329-3

## Contents

| 1. | An   | $\operatorname{Introd}$ | uction to GPU Computing             | 1  |

|----|------|-------------------------|-------------------------------------|----|

|    | 1.1. | The C                   | UDA Programming and Execution Model | 1  |

|    |      | 1.1.1.                  | SM Resource Partition               | 6  |

|    | 1.2. | Efficie                 | nt Memory Accesses in CUDA          | 7  |

|    |      | 1.2.1.                  | Global Memory Accesses              | 8  |

|    |      | 1.2.2.                  | Shared Memory Accesses              | 9  |

|    |      | 1.2.3.                  | Shuffle Instructions                | 10 |

|    |      | 1.2.4.                  | Atomic Operations                   | 11 |

|    | 1.3. | Multip                  | ole-GPU Programming                 | 11 |

|    | 1.4. | CUDA                    | A Architectures                     | 13 |

|    |      | 1.4.1.                  | Fermi Architecture                  | 13 |

|    |      | 1.4.2.                  | Kepler Architecture                 | 14 |

|    |      | 1.4.3.                  | Maxwell Architecture                | 16 |

|    |      | 1.4.4.                  | Pascal Architecture                 | 17 |

|    |      | 1.4.5.                  | Volta Architecture                  | 19 |

| 2. | Para | allel P                 | refix Algorithms                    | 23 |

XXX Contents

|    | 2.1. | Paralle                                                              | el Prefix Definitions                                          | 23 |

|----|------|----------------------------------------------------------------------|----------------------------------------------------------------|----|

|    |      | 2.1.1.                                                               | Index-Digit Algorithms                                         | 24 |

|    | 2.2. | Fast F                                                               | ourier Transform (FFT)                                         | 27 |

|    |      | 2.2.1.                                                               | The Real Fourier Transform                                     | 30 |

|    | 2.3. | Tridiag                                                              | gonal System Solvers                                           | 31 |

|    |      | 2.3.1.                                                               | Thomas Algorithm                                               | 33 |

|    |      | 2.3.2.                                                               | Parallel Algorithms for Solving Tridiagonal Systems            | 34 |

|    |      | 2.3.3.                                                               | The Partitioning Problem                                       | 38 |

|    | 2.4. | Scan C                                                               | Operator                                                       | 40 |

|    |      | 2.4.1.                                                               | Brent-Kung Pattern                                             | 41 |

|    |      | 2.4.2.                                                               | Kogge-Stone Pattern (KS)                                       | 42 |

|    |      | 2.4.3.                                                               | Han-Carlson Pattern                                            | 43 |

|    |      | 2.4.4.                                                               | Ladner-Fischer Pattern                                         | 44 |

|    | 2.5. | Sorting                                                              | g Algorithms                                                   | 44 |

|    | 2.6. | CUDA                                                                 | Notation for Paralell Prefix Algorithms                        | 47 |

| 3. | New  | v Paral                                                              | llel Prefix Algorithms                                         | 49 |

|    | 3.1. | Redundant Reduction: A New Algorithm for Solving Tridiagonal Systems |                                                                |    |

|    |      | 3.1.1.                                                               | The Redundant Reduction Operation                              | 50 |

|    |      | 3.1.2.                                                               | Redundant Reduction Algorithm using the Kogge-Stone Pattern    | 52 |

|    |      | 3.1.3.                                                               | Redundant Reduction Algorithm using the Ladner-Fischer Pattern | 54 |

|    |      | 3 1 4                                                                | Experimental Results for the RR operation in CUDA              | 55 |

Contents

|      |                                                            | Partitioning Reduction: A New Algorithm for Solving Tridiagystems                                                                                       | 62                                         |  |  |

|------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

|      | 3.2.1.                                                     | The TPR Forward Reduction phase                                                                                                                         | 62                                         |  |  |

|      | 3.2.2.                                                     | The TPR Backward Substitution phase                                                                                                                     | 69                                         |  |  |

|      | 3.2.3.                                                     | An example of the TPR method                                                                                                                            | 69                                         |  |  |

| 3.3. | Bitoni                                                     | c Merge Comb Sort: A New Algorithm for Sorting                                                                                                          | 70                                         |  |  |

|      | 3.3.1.                                                     | A CUDA Implementation for the Bitonic Merge Sort Algorithm                                                                                              | 71                                         |  |  |

|      | 3.3.2.                                                     | Bitonic Merge Comb Sort                                                                                                                                 | 72                                         |  |  |

|      | 3.3.3.                                                     | Experimental Results for BMCS in CUDA                                                                                                                   | 76                                         |  |  |

| 3.4. | Conclu                                                     | asions of the Chapter                                                                                                                                   | 79                                         |  |  |

| АТ   | uning                                                      | Methodology for Small Problem Sizes on a GPU                                                                                                            | 81                                         |  |  |

| 4.1. | GPU I                                                      | Resource Utilization Analysis Phase                                                                                                                     | 82                                         |  |  |

|      | 4.1.1.                                                     | Premises for Performance Maximization                                                                                                                   | 83                                         |  |  |

| 4.2. | CUDA                                                       | Kernel Optimization Phase                                                                                                                               | 84                                         |  |  |

| 4.3. | Performance Parameter Tuning Phase                         |                                                                                                                                                         |                                            |  |  |

| 4.4. | Tridiagonal System Solvers under a three-phase methodology |                                                                                                                                                         |                                            |  |  |

|      | 4.4.1.                                                     | Cyclic Reduction Tridiagonal System Solver (BPLG-CR-TS Algorithm)                                                                                       | 89                                         |  |  |

|      | 4.4.2.                                                     | Parallel Cyclic Reduction Tridiagonal System Solver (BPLG-PCR-TS Algorithm)                                                                             | 93                                         |  |  |

|      | 4.4.3.                                                     | Ladner-Fischer Tridiagonal System Solver (BPLG-LF-TS Algorithm)                                                                                         | 98                                         |  |  |

|      | 4.4.4.                                                     | Experimental Results for Tridiagonal System Solvers with Small Problem Sizes                                                                            | 100                                        |  |  |

| 4.5. | Scan                                                       | Primitive under a three-phase methodology                                                                                                               | 108                                        |  |  |

|      | 3.4. <b>A T</b> 4.1. 4.2. 4.3. 4.4.                        | 3.2.1. 3.2.2. 3.2.3. 3.3. Bitonic 3.3.1. 3.3.2. 3.3.3. 3.4. Conclus A Tuning 4.1. GPU I 4.1.1. 4.2. CUDA 4.3. Perfor 4.4. 4.4.1. 4.4.2. 4.4.3. 4.4.4.3. | 3.2.2. The TPR Backward Substitution phase |  |  |

XXXII Contents

|    |      | 4.5.1.                                                                                           | Scan operator using the Ladner-Fischer pattern (BPLG-LF-SC Algorithm) |  |  |  |

|----|------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

|    |      | 4.5.2.                                                                                           | Scan operator using Kogge-Stone pattern (BPLG-KS-SC Algorithm)        |  |  |  |

|    |      | 4.5.3.                                                                                           | Experimental Results for the Scan Primitive with Small Problem Sizes  |  |  |  |

|    | 4.6. | Sortin                                                                                           | g under a three-phase methodology (BPLG-BMCS Algorithm) . 119         |  |  |  |

|    |      | 4.6.1.                                                                                           | CUDA Kernel Optimization phase: BPLG-BMCS 122                         |  |  |  |

|    |      | 4.6.2.                                                                                           | Performance Parameter Tuning phase: BPLG-BMCS 122                     |  |  |  |

|    |      | 4.6.3.                                                                                           | Experimental Results for Sorting with Small Problem Sizes 123         |  |  |  |

|    | 4.7. | Conclu                                                                                           | usions of the Chapter                                                 |  |  |  |

| 5. |      | A Tuning Methodology for Parallel Prefix Algorithms on a GPU: Medium and Large Problem Sizes 129 |                                                                       |  |  |  |

|    | 5.1. | A two                                                                                            | -phase Methodology for Index-Digit Algorithms                         |  |  |  |

|    |      | 5.1.1.                                                                                           | GPU Resources Utilization Analysis Phase                              |  |  |  |

|    |      | 5.1.2.                                                                                           | CUDA Kernel Optimization Phase: String Operators and Map-             |  |  |  |

|    | 5.2. |                                                                                                  | ping Vector                                                           |  |  |  |

|    |      |                                                                                                  | ping Vector                                                           |  |  |  |

|    |      | ID-TS                                                                                            | Stage Index-Digit Tridiagonal System Solver Algorithm (MS-            |  |  |  |

|    | 5.3. | <ul><li>ID-TS</li><li>5.2.1.</li><li>Experi</li></ul>                                            | Stage Index-Digit Tridiagonal System Solver Algorithm (MS-)           |  |  |  |

|    |      | ID-TS 5.2.1. Experis                                                                             | Stage Index-Digit Tridiagonal System Solver Algorithm (MS-)           |  |  |  |

|    |      | ID-TS 5.2.1. Experisives Sizes A three                                                           | Stage Index-Digit Tridiagonal System Solver Algorithm (MS-)           |  |  |  |

Contents

|            |              | 5.4.3.                                      | Performance Parameter Tuning                                                                                                                                                                                                                                                                                                       | 154                             |

|------------|--------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|            | 5.5.         | Scan I                                      | Primitive based on Ladner-Fischer                                                                                                                                                                                                                                                                                                  | 154                             |

|            |              | 5.5.1.                                      | CUDA Kernel Optimization: Scan-SP                                                                                                                                                                                                                                                                                                  | 156                             |

|            |              | 5.5.2.                                      | Performance Parameter Tuning: Scan-SP                                                                                                                                                                                                                                                                                              | 159                             |

|            | 5.6.         | Tridia                                      | gonal System Solver based on the Tree Partitioning Reduction .                                                                                                                                                                                                                                                                     | 161                             |

|            |              | 5.6.1.                                      | CUDA Kernel Optimization: $TPR$                                                                                                                                                                                                                                                                                                    | 162                             |

|            |              | 5.6.2.                                      | Performance Parameter Tuning: TPR                                                                                                                                                                                                                                                                                                  | 164                             |

|            | 5.7.         | _                                           | imental Results for Parallel Prefix Algorithms with Medium-<br>Problem Sizes                                                                                                                                                                                                                                                       | 167                             |

|            |              | 5.7.1.                                      | Scan Primitive                                                                                                                                                                                                                                                                                                                     | 167                             |

|            |              | 5.7.2.                                      | Tridiagonal Systems                                                                                                                                                                                                                                                                                                                | 169                             |

|            | F 0          | Concl                                       | usions of the Chapter                                                                                                                                                                                                                                                                                                              | 177                             |

|            | 5.8.         | Concr                                       | asions of the Chapter                                                                                                                                                                                                                                                                                                              | 111                             |

| 3.         |              |                                             |                                                                                                                                                                                                                                                                                                                                    |                                 |

| 3.         | Pa           | rallel                                      | Prefix Algorithms on Multiple-GPU systems: Dealing                                                                                                                                                                                                                                                                                 |                                 |

| 5.         | Pa           | rallel<br>n Extr<br>A Tur                   | Prefix Algorithms on Multiple-GPU systems: Dealing                                                                                                                                                                                                                                                                                 | 179                             |

| б.         | Pa<br>with   | rallel<br>n Extr<br>A Tur<br>GPU            | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-                                                                                                                                                                                         | 1 <b>79</b><br>180              |

| 3.         | Pa with 6.1. | rallel<br>n Extr<br>A Tur<br>GPU            | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-Environments                                                                                                                                                                             | 1 <b>79</b><br>180<br>184       |

| <b>3</b> . | Pa with 6.1. | rallel A Tur GPU A Mu 6.2.1.                | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-Environments                                                                                                                                                                             | 180<br>184<br>184               |

| 3.         | Pa with 6.1. | rallel A Tur GPU A Mu 6.2.1.                | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-Environments                                                                                                                                                                             | 180<br>184<br>184<br>185        |

| 6.         | Pa with 6.1. | A Tur<br>GPU :<br>A Mu:<br>6.2.1.<br>6.2.2. | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-Environments  tiple-GPU Strategy for the Scan Operator  Multi-GPU Batch Parallelism (MBP)  Multi-GPU Problem Scattering (MPS)  Multi-GPU Problem with Prioritized Communications (MP-    | 180<br>184<br>184<br>185        |

| 3.         | Pa with 6.1. | A Tur GPU A Mu 6.2.1. 6.2.2. 6.2.3.         | Prefix Algorithms on Multiple-GPU systems: Dealing emely Large Problem Sizes  aing Methodology for Parallel Prefix Algorithms on Multiple-Environments  tiple-GPU Strategy for the Scan Operator  Multi-GPU Batch Parallelism (MBP)  Multi-GPU Problem Scattering (MPS)  Multi-GPU Problem with Prioritized Communications (MP-PC) | 180<br>184<br>184<br>185<br>187 |

XXXIV Contents

|    |      | 6.3.2. Multi-Node Environment                                                                 |

|----|------|-----------------------------------------------------------------------------------------------|

|    | 6.4. | A Multiple-GPU Strategy for Index-Digit Algorithms on Multiple-GPU Environments               |

|    |      | 6.4.1. A Two-phase Tuning Methodology 198                                                     |

|    | 6.5. | A Multiple-GPU Strategy for a Tridiagonal System Solver 200                                   |

|    |      | 6.5.1. Multi-GPU Batch Parallelism (MBP) 200                                                  |

|    |      | 6.5.2. Multi-GPU Problem Scattering (MPS) 205                                                 |

|    |      | 6.5.3. Multi-GPU Problem with Prioritized Communications (MP-PC)                              |

|    |      | 6.5.4. Performance Maximization of the Tridiagonal System Approaches 209                      |

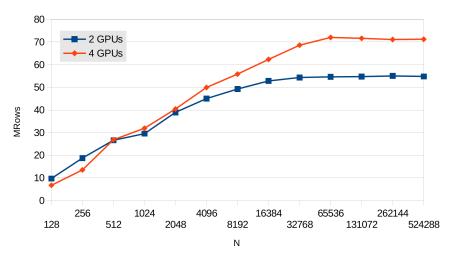

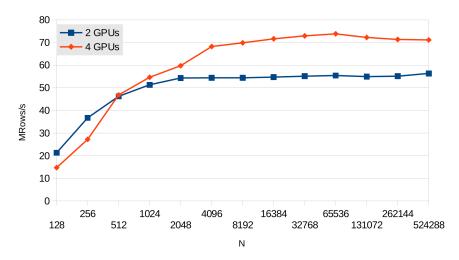

|    | 6.6. | Experimental Results for the Tridiagonal System Solver with Extremely-<br>Large Problem Sizes |

|    |      | 6.6.1. Batch Parallelism                                                                      |

|    |      | 6.6.2. Problem Parallelism                                                                    |

|    | 6.7. | Conclusions of the Chapter                                                                    |

| 7. | Usiı | ng Accelerated Parallel Prefix Operations on Real Applications 219                            |

|    | 7.1. | Introduction to High-Precision Integers                                                       |

|    | 7.2. | The Strassen FFT Multiplication Algorithm                                                     |

|    | 7.3. | The CUDA FFT-based Multiplication Approach                                                    |

|    |      | 7.3.1. The Complex-ID Proposal                                                                |

|    |      | 7.3.2. The Real-ID Proposal                                                                   |

|    | 7.4. | The CUDA Tiling Multiplication Approach                                                       |

|    |      | 7.4.1. The vector convolution algorithm                                                       |

|    |      | 7.4.2. CUDA implementation                                                                    |

| Content | S      |                                                       | <br>XXXV  |

|---------|--------|-------------------------------------------------------|-----------|

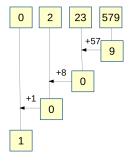

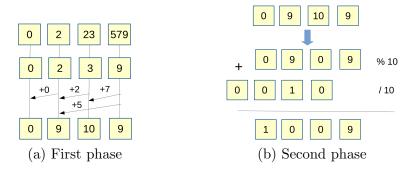

| 7.5.    | The C  | darry Normalization                                   | <br>. 227 |

| 7.6.    | Exper  | imental Results for the High-Precision Multiplication | <br>. 230 |

|         | 7.6.1. | Numerical analysis                                    | <br>. 231 |

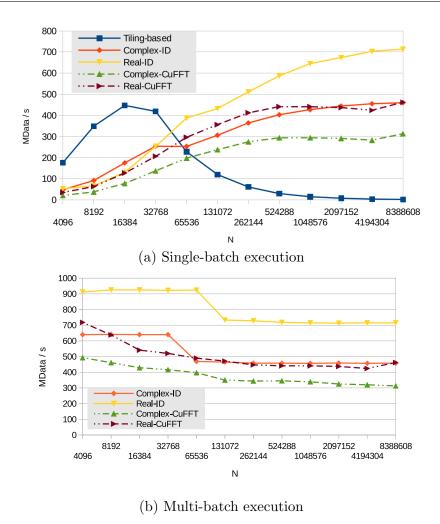

|         | 7.6.2. | Performance analysis                                  | <br>. 232 |

|         | 7.6.3. | Results Discussion                                    | <br>. 240 |

| 7.7.    | Concl  | usions of the Chapter                                 | <br>. 242 |

| 8. Con  | clusio | ns and Future Work                                    | 245       |

| Refere  | nces   |                                                       | 253       |

| A. Res  | umo E  | Stendido en Galego                                    | 267       |

## List of Tables

| 2.1. | Classification of the algorithms employed in this work                                        | 26  |

|------|-----------------------------------------------------------------------------------------------|-----|

| 2.2. | Description of the GPU parameters used                                                        | 48  |

| 3.1. | Description of the test platforms for the RR algorithms                                       | 56  |

| 3.2. | Kernel profile analysis of our proposals on the Kernel Platform $$                            | 63  |

| 3.3. | Description of the test platforms for the sorting problem                                     | 76  |

| 3.4. | MData/s comparison of GPU multi-batch sorting algorithms                                      | 80  |

| 3.5. | GPU parameters and profiling metrics for our sorting proposals                                | 80  |

| 4.1. | Description of tuning strategy parameters                                                     | 83  |

| 4.2. | Performance parameters which maximize the number of warps and blocks per SM                   | 87  |

| 4.3. | Description of tridiagonal tuning parameters                                                  | 93  |

| 4.4. | Description of the test platforms                                                             | 101 |

| 4.5. | BPLG-LF-TS occupancies                                                                        | 106 |

| 4.6. | Performance comparison of different performance parameters values for BPLG-LF-TS in MRows / s | 109 |

| 4.7. | Description of the LF scan tuning parameters                                                  | 112 |

| 4.8. | Description of the KS scan tuning parameters                                                  | 115 |

XXXVIII List of Tables

| 4.9.  | Performance comparison of different performance parameters values for BPLG-LF-SC in MData / s |

|-------|-----------------------------------------------------------------------------------------------|

| 4.10. | Description of the BPLG-BMCS sorting tuning parameters 123                                    |

| 4.11. | MData/s comparison of GPU multi-batch Sorting Algorithms in the Maxwell Platform              |

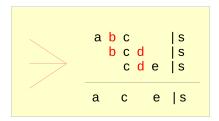

| 5.1.  | Description of string operators                                                               |

| 5.2.  | Description of the test platforms                                                             |

| 5.3.  | Complex MS-ID-TS kernel performance and profiler analysis (Kepler K20 Platform)               |

| 5.4.  | Complex MS-ID-TS kernel performance and profiler analysis (Maxwell Platform)                  |

| 5.5.  | Description of the performance parameters for parallel prefix algorithms                      |

| 5.6.  | Performance parameters per SM on Kepler Platforms with compute capability 3.7                 |

| 5.7.  | Description of tuning parameters, where $S = P \cdot L$ and $P = 2$ 165                       |

| 5.8.  | Description of the test platform                                                              |

| 5.9.  | Relative error of the two FP32-TPR configurations for a Topletz matrix 175                    |

| 5.10. | Matrix types used in the numerical evaluation from [74] 175                                   |

| 5.11. | Relative errors for FP32                                                                      |

| 5.12. | Relative errors for FP64                                                                      |

| 6.1.  | Description of tuning strategy parameters                                                     |

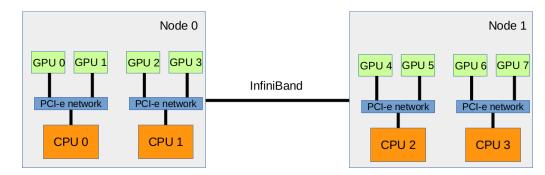

| 6.2.  | Description of a computing node in the test platform                                          |

| 6.3.  | Description of the performance parameters for ID-algorithms in Multiple-GPU                   |

| List of Tables                                       | XXXIX |

|------------------------------------------------------|-------|

| 6.4. Description of the test platforms               | 211   |

| 7.1. Description of the computing platforms employed | 231   |

| 7.2. Numerical analysis for our FFT proposals        | 232   |

## List of Figures

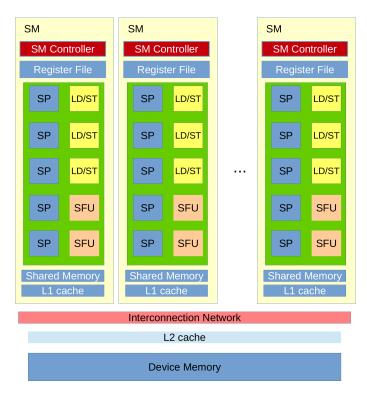

| 1.1.  | A GPU composed of an array of Streaming Multiprocessors (SM)                               | 3  |

|-------|--------------------------------------------------------------------------------------------|----|

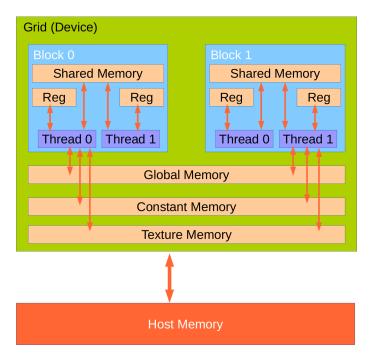

| 1.2.  | CUDA memory subsystem                                                                      | 5  |

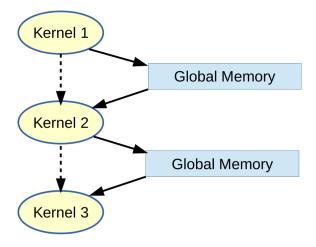

| 1.3.  | Communication among kernels across global memory                                           | 5  |

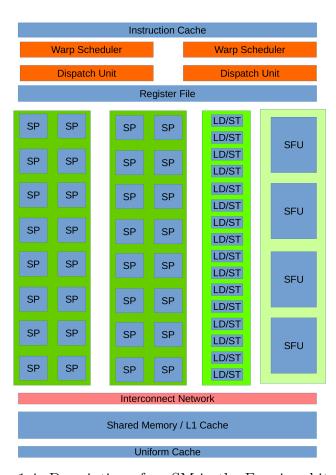

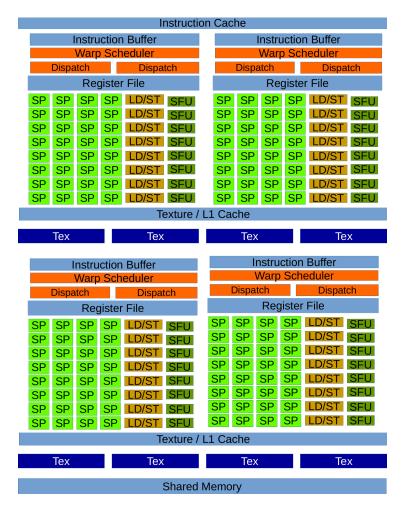

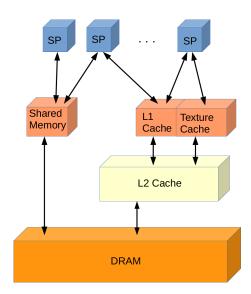

| 1.4.  | Description of an SM in the Fermi architecture                                             | 14 |

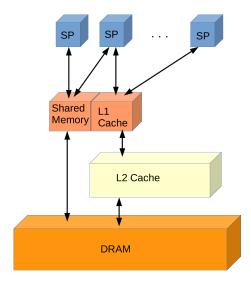

| 1.5.  | Description of the Fermi memory subsystem                                                  | 15 |

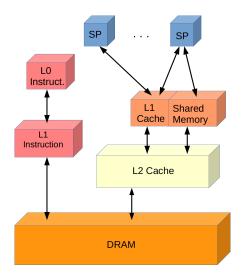

| 1.6.  | Description of an SM in the Kepler architecture                                            | 15 |

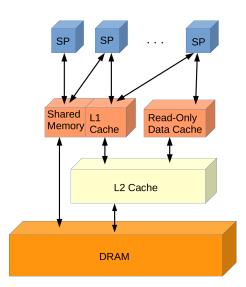

| 1.7.  | Description of the Kepler memory subsystem                                                 | 16 |

| 1.8.  | Description of an SM in the Maxwell architecture                                           | 17 |

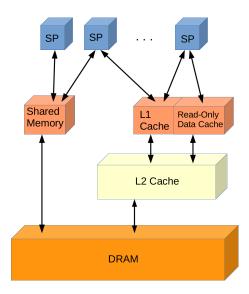

| 1.9.  | Description of the Maxwell memory subsystem                                                | 18 |

| 1.10. | Description of an SM in the Pascal architecture                                            | 18 |

| 1.11. | Description of the Pascal memory subsystem                                                 | 19 |

| 1.12. | Description of an SM in the Volta architecture                                             | 20 |

| 1.13. | Description of the Volta memory subsystem                                                  | 21 |

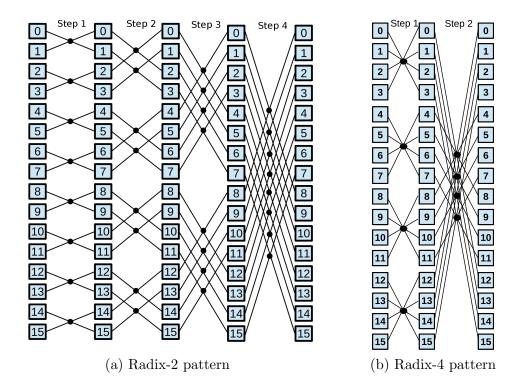

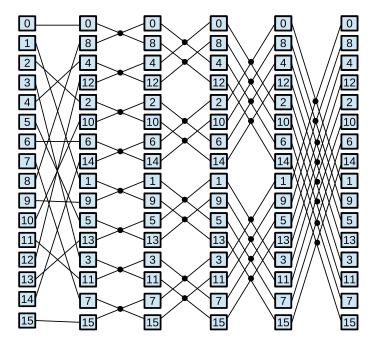

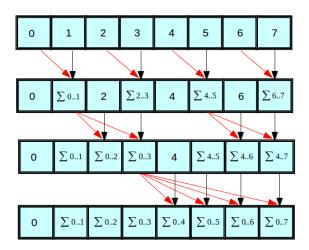

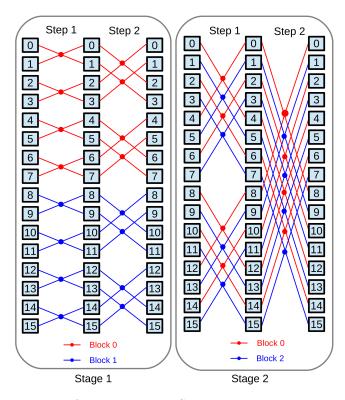

| 2.1.  | A parallel prefix algorithm, Cooley-Tukey, with $N=16.\dots\dots$                          | 24 |

| 2.2.  | Difference between an Index-Digit algorithm (a) and a Parallel Prefix non-ID algorithm (b) | 26 |

| 2.3.  | Examples of FFT algorithms with $r=2$ and $N=16.\ldots$                                    | 29 |

XLII List of Figures

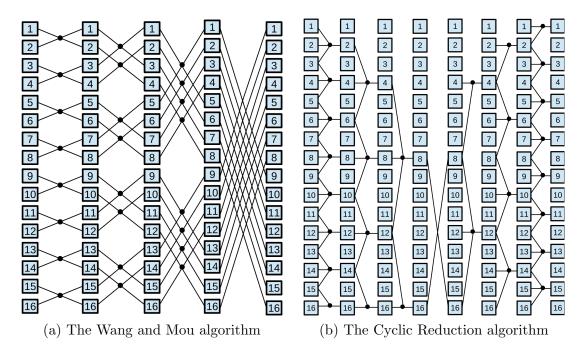

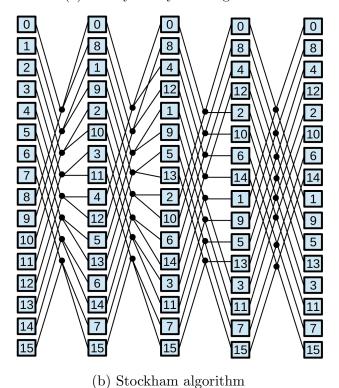

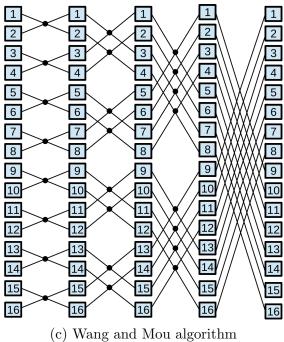

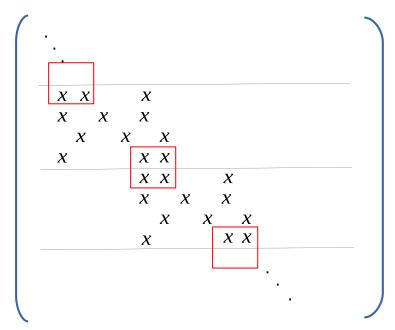

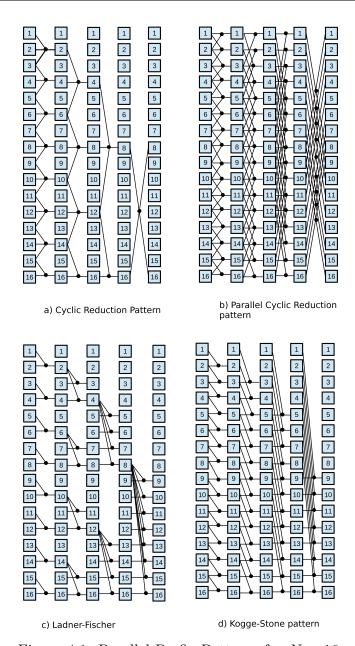

| 2.4.                         | Patterns for different tridiagonal system solvers with $N=16$ elements.                                                                                   | 37                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 2.5.                         | Reduction of two triads in the Wang and Mou algorithm                                                                                                     | 38                                         |

| 2.6.                         | Cyclic Reduction example for $N=16$ elements                                                                                                              | 39                                         |

| 2.7.                         | Equation dependencies among slices in the coefficient matrix for the Cyclic Reduction algorithm                                                           | 40                                         |

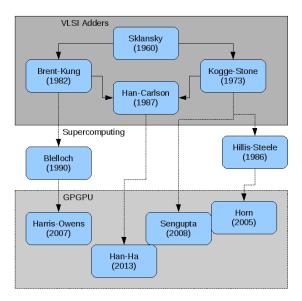

| 2.8.                         | Taxonomy of the existing parallel algorithms for scan operator based on VLSI adders                                                                       | 42                                         |

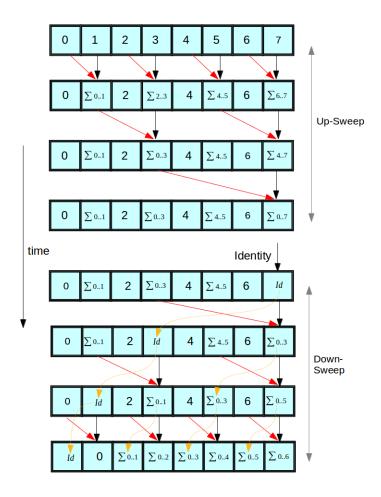

| 2.9.                         | Brent-Kung pattern for addition with $N=8.$                                                                                                               | 43                                         |

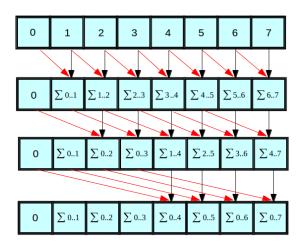

| 2.10.                        | . Kogge-Stone pattern for addition with $N=8.$                                                                                                            | 44                                         |

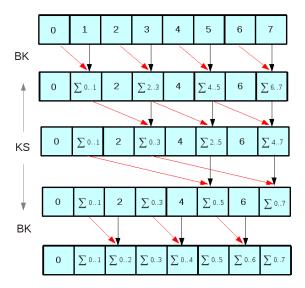

| 2.11.                        | . Han-Carlson pattern for addition with $N=8$                                                                                                             | 45                                         |

| 2.12.                        | . Ladner-Fischer pattern for addition with $N=8.$                                                                                                         | 46                                         |

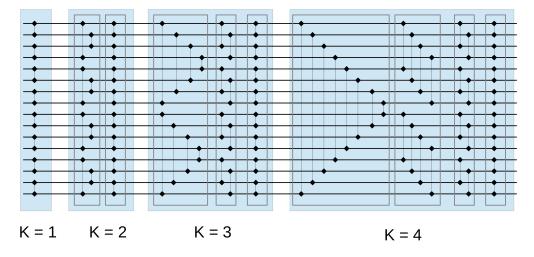

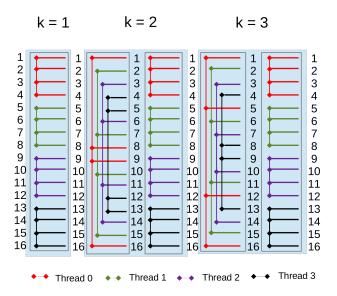

| 2.13.                        | . Bitonic Merge Sort Algorithm with $N=16.\dots\dots$                                                                                                     | 46                                         |

|                              |                                                                                                                                                           |                                            |

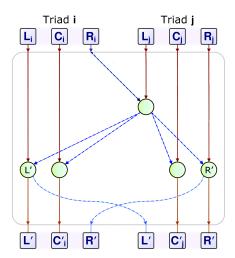

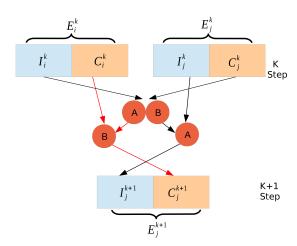

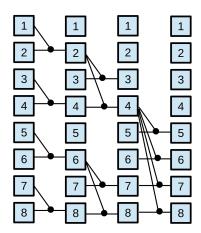

| 3.1.                         | Redundant Reduction scheme for $E_i^k$ and $E_j^k$ where $A,B$ circles denote the resulting equation of applying Reduction A or Reduction B, respectively | 52                                         |

| 3.1.<br>3.2.                 | note the resulting equation of applying $Reduction A$ or $Reduction B$ ,                                                                                  |                                            |

|                              | note the resulting equation of applying $Reduction\ A$ or $Reduction\ B$ , respectively                                                                   | 53                                         |

| 3.2.<br>3.3.                 | note the resulting equation of applying $Reduction\ A$ or $Reduction\ B$ , respectively                                                                   | 53<br>53                                   |

| 3.2.<br>3.3.                 | note the resulting equation of applying $Reduction\ A$ or $Reduction\ B$ , respectively                                                                   | 53<br>53                                   |

| 3.2.<br>3.3.<br>3.4.         | note the resulting equation of applying $Reduction\ A$ or $Reduction\ B$ , respectively                                                                   | 53<br>53                                   |

| 3.2.<br>3.3.<br>3.4.<br>3.5. | note the resulting equation of applying $Reduction\ A$ or $Reduction\ B$ , respectively                                                                   | <ul><li>53</li><li>55</li><li>57</li></ul> |

List of Figures XLIII

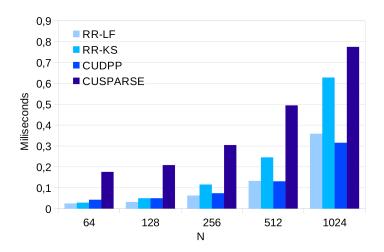

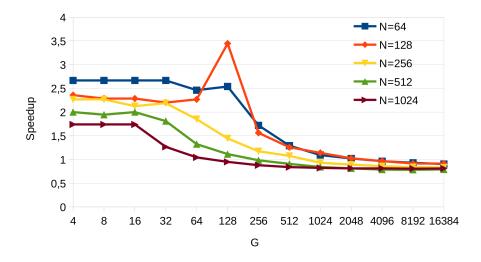

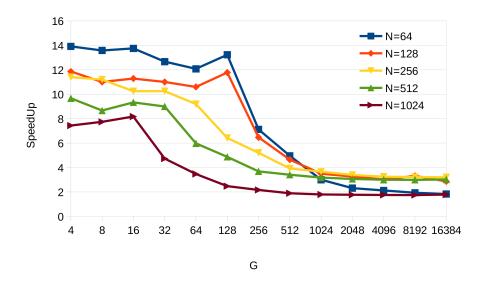

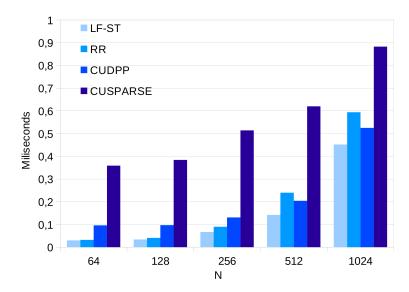

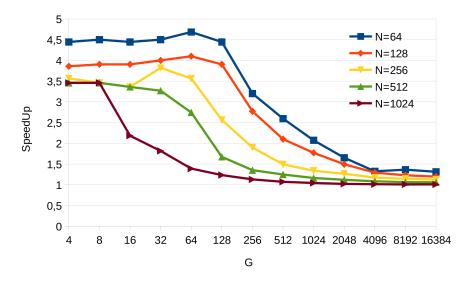

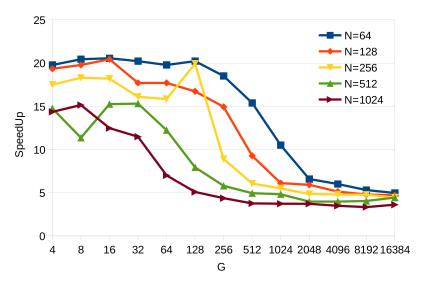

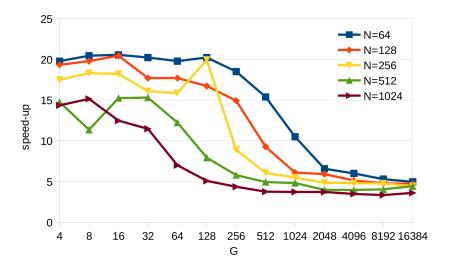

| 3.9. $RR$ - $LF$ speed-up over $CUDPP$ for different $G$ batch sizes on Kepler Platform              | 60         |

|------------------------------------------------------------------------------------------------------|------------|

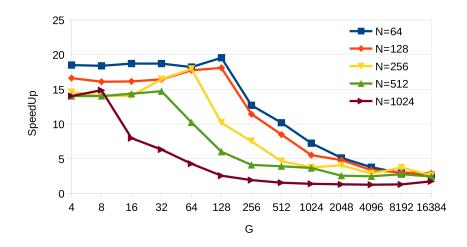

| 3.10. $RR\text{-}LF$ speed-up over $CUSPARSE$ for different $G$ batch sizes on Kepler Platform.      | 61         |

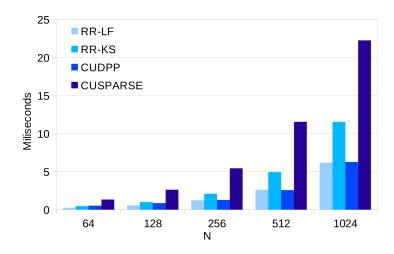

| 3.11. Performance results on the Maxwell Platform for $G=256\ batches$ 6                             | 61         |

| 3.12. $RR\text{-}LF$ speed-up for different $G$ batch sizes over $CUDPP$ on the Maxwell architecture | 63         |

| 3.13. $RR$ - $LF$ speed-up for different $G$ batch sizes over $CUSPARSE$ on the Maxwell architecture | 64         |

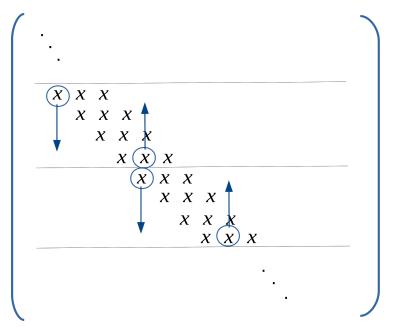

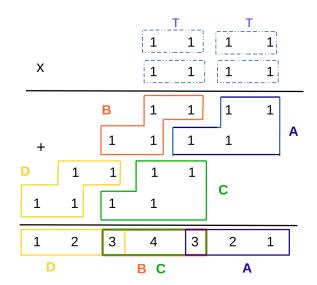

| 3.14. Forward reduction phase for $N=16$ elements in the TPR method . 6                              | 64         |

| 3.15. Coefficient matrix evolution in the TPR method                                                 | 65         |

| 3.16. Tree Partitioning Reduction example for $N=16$ elements with $S=8$                             | 67         |

| 3.17. Coefficient reductions in the TPR forward reduction phase for a node computation               | 68         |

| 3.18. Kernel code for Bitonic Merge Sort algorithm (BS-naive)                                        | 72         |

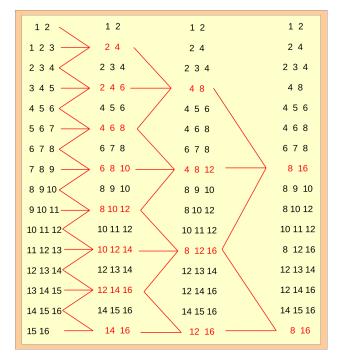

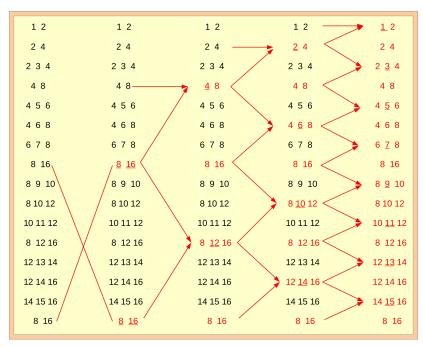

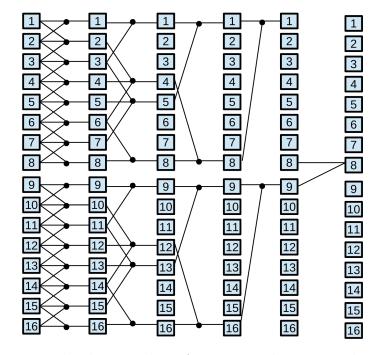

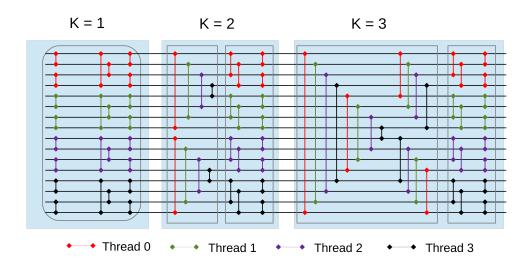

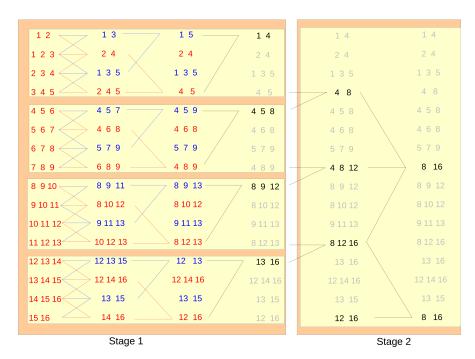

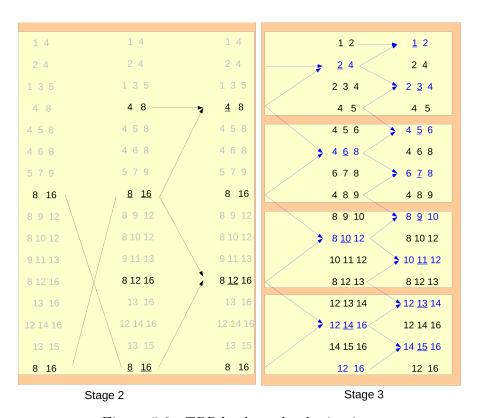

| 3.19. Bitonic Merge Comb Sort Algorithm with $N=16.\ldots$ 7                                         | 74         |

| 3.20. Bitonic Merge Comb Sort Algorithm for $N=16.$                                                  | <b>7</b> 5 |

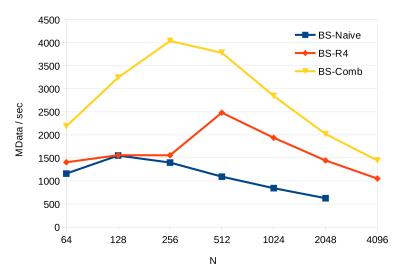

| 3.21. Comparison of our proposal optimizations in the Kepler Platform $7$                            | 77         |

| 3.22. Comparison of our proposal optimizations in the Maxwell Platform $7$                           | 77         |

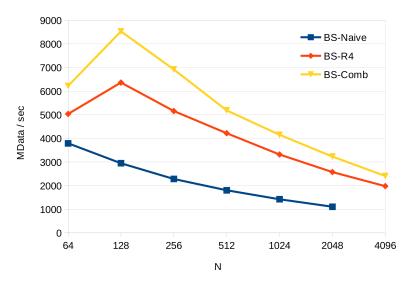

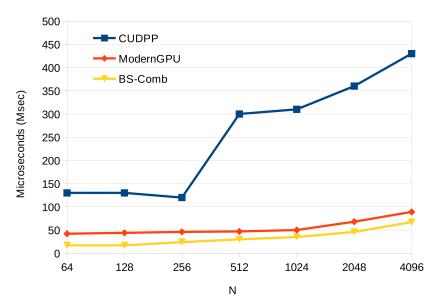

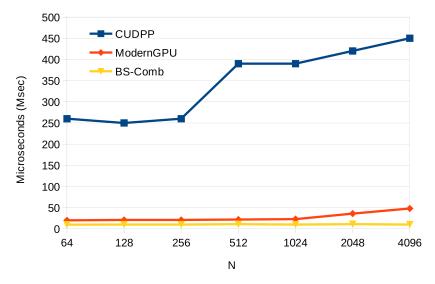

| 3.23. Comparison of GPU sorting implementations for one batch in the Kepler Platform                 | 78         |

| 3.24. Comparison of GPU sorting implementations for one batch in the Maxwell Platform                | 78         |

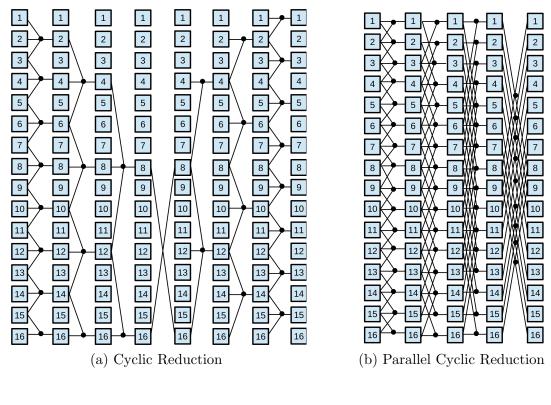

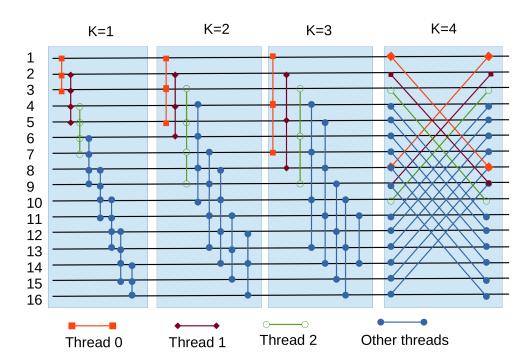

| 4.1. Parallel Prefix Patterns for $N = 16$                                                           | 90         |

| 4.2. Forward Reduction code for CR tridiagonal algorithm using BPLG 9                                | 91         |

XLIV List of Figures

| 4.3.  | Code for the PCR tridiagonal algorithm in BPLG                                                                  | 94  |

|-------|-----------------------------------------------------------------------------------------------------------------|-----|

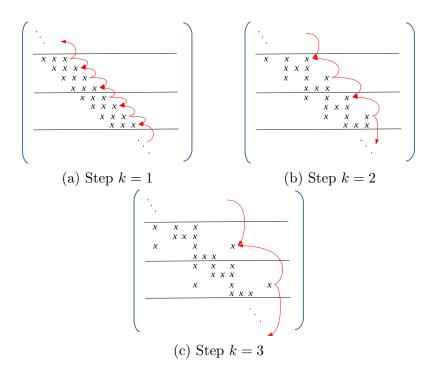

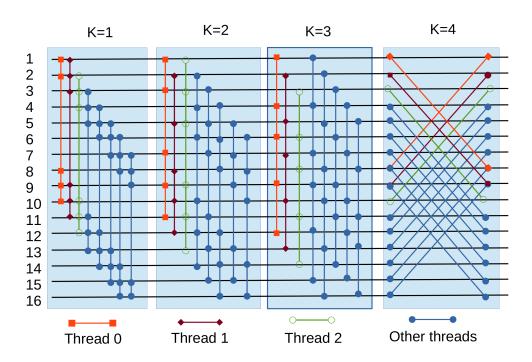

| 4.4.  | Operator nodes allocation for the PCR algorithm with $N=16.$                                                    | 95  |

| 4.5.  | Operator nodes for the PCR algorithm with $N=16$ using the <i>Efficient Allocation</i> strategy                 | 96  |

| 4.6.  | PCR dependences when applying the Equation-warp matching with $N=16. \ldots \ldots \ldots \ldots \ldots \ldots$ | 97  |

| 4.7.  | Code for LF tridiagonal algorithm in BPLG                                                                       | 99  |

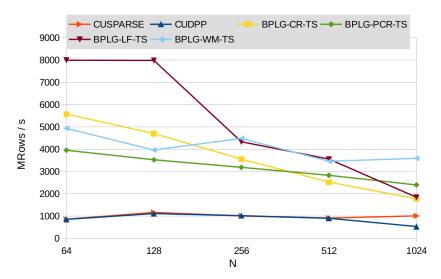

| 4.8.  | MRows/s comparison of the CR tridiagonal proposals in the Kepler Platform.                                      | 102 |

| 4.9.  | MRows/s comparison of the CR tridiagonal proposals in the Maxwell Platform.                                     | 102 |

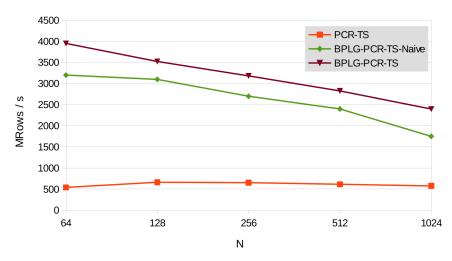

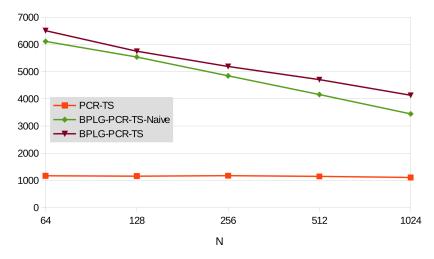

| 4.10. | . MRows/s comparison of the PCR tridiagonal implementations in the Kepler Platform                              | 104 |

| 4.11. | MRows/s comparison of the PCR tridiagonal implementations in the Maxwell Platform.                              | 104 |

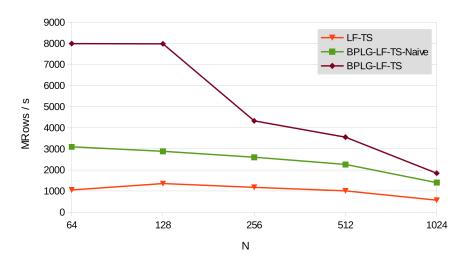

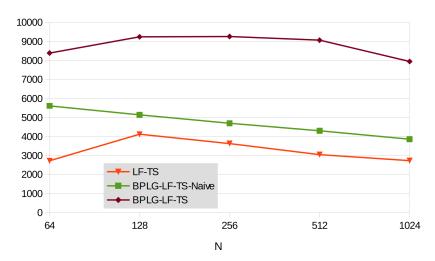

| 4.12. | . MRows/s comparison of LF tridiagonal implementations in the Kepler Platform.                                  | 105 |

| 4.13. | . MRows/s comparison of LF tridiagonal implementations in the Maxwell Platform.                                 | 106 |

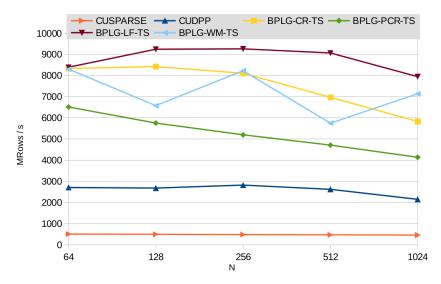

| 4.14. | Comparison of BPLG tridiagonal solvers performance in the Kepler Platform.                                      | 107 |

| 4.15. | . Comparison of BPLG tridiagonal solvers performance in the Maxwell Platform.                                   | 107 |

| 4.16. | . Kernel code for the LF-scan algorithm in BPLG.                                                                | 110 |

| 4.17. | . Kernel code for KS scan algorithm in BPLG.                                                                    | 113 |

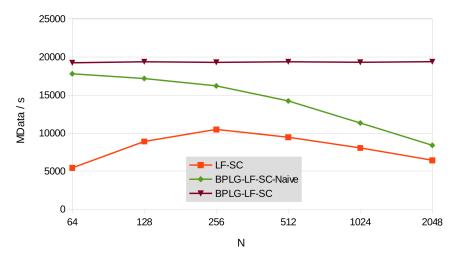

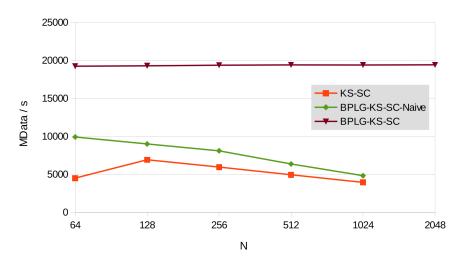

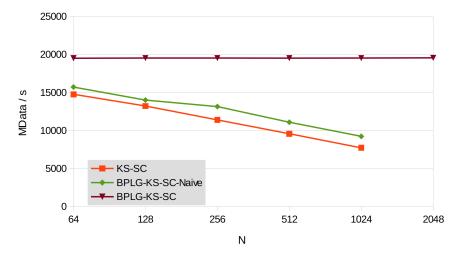

| 4.18. | . MData/s comparison of BPLG-LF scan implementations in the Kepler Platform.                                    | 115 |

List of Figures XLV

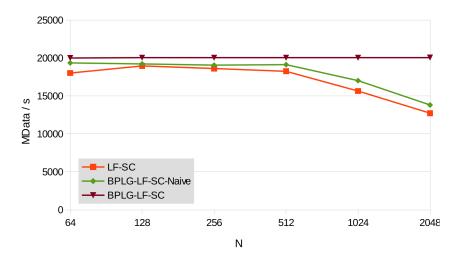

| 4.19. MData/s comparison of BPLG-LF scan implementations in the Maxwell Platform                      | 16 |

|-------------------------------------------------------------------------------------------------------|----|

| 4.20. MData/s comparison of BPLG-KS scan implementations in the Kepler Platform                       | 17 |

| 4.21. MData/s comparison of BPLG-KS scan implementations in the Maxwell Platform                      | 17 |

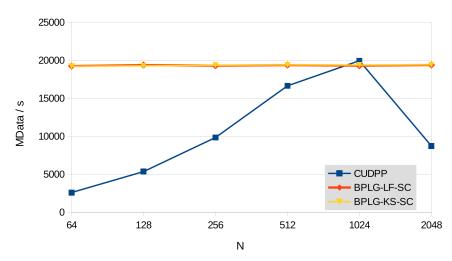

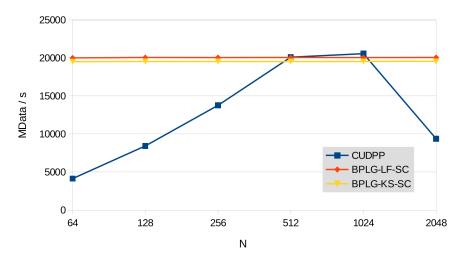

| 4.22. MData/s performance comparison of BPLG scan proposals in the Kepler Platform                    | 18 |

| 4.23. MData/s performance comparison of BPLG scan proposals in the Maxwell Platform                   | 18 |

| 4.24. Kernel code for the BMCS algorithm using BPLG skeletons 12                                      | 21 |

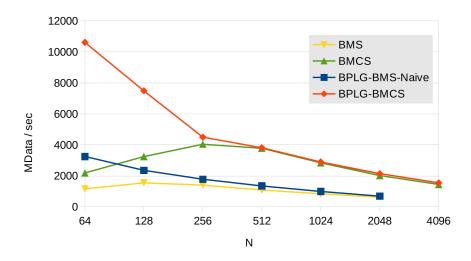

| 4.25. Comparison of our proposals in the Kepler Platform                                              | 24 |

| 4.26. Comparison of our proposals in the Maxwell Platform                                             | 25 |

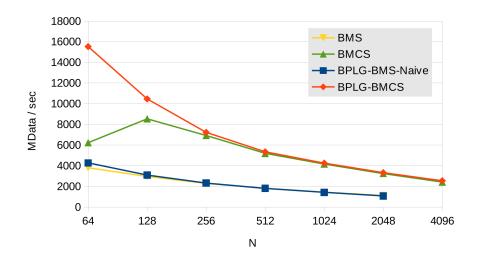

| 4.27. Comparison of GPU sorting implementations for one batch on the Kepler Platform                  | 26 |

| 4.28. Comparison of GPU sorting implementations for one batch on the Maxwell Platform                 | 27 |

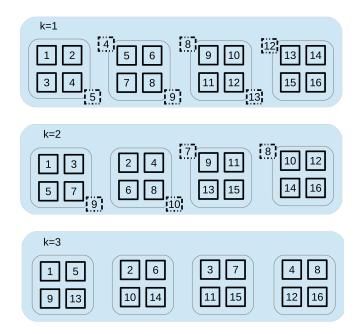

| 5.1. Data mapping with $r = 2$ , $n = 11$ , $s = 9$ , $p = 4$ and $b_x = 2$ 13                        | 37 |

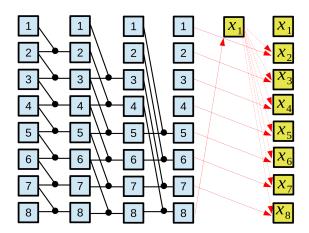

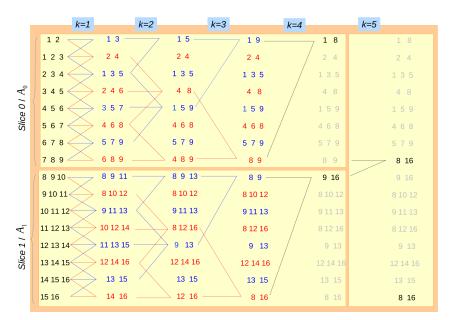

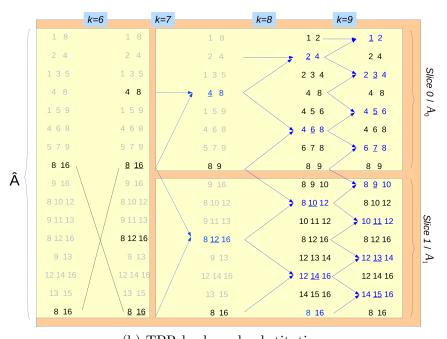

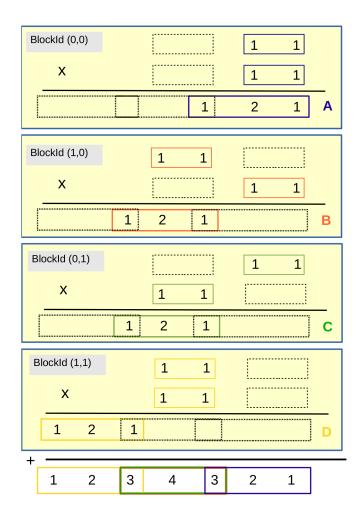

| 5.2. Distribution of the $ID$ - $LD$ - $TS$ proposal with two stages for $N=16$ , $p=l=1$ and $b_x=2$ | 41 |

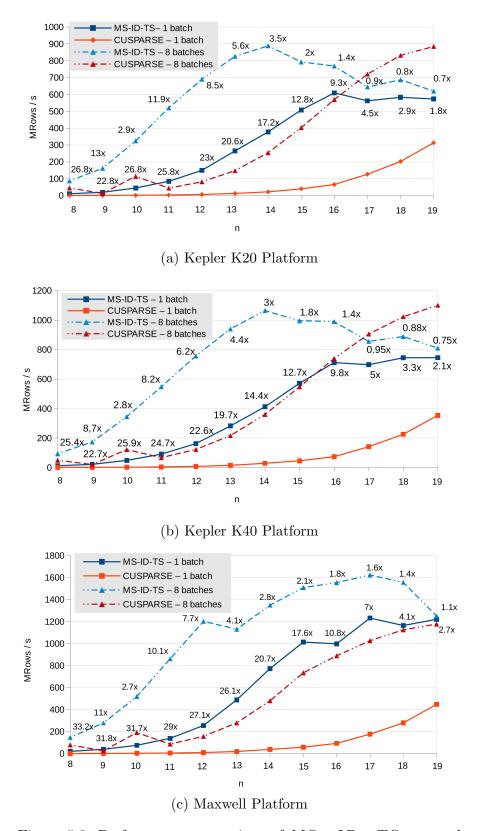

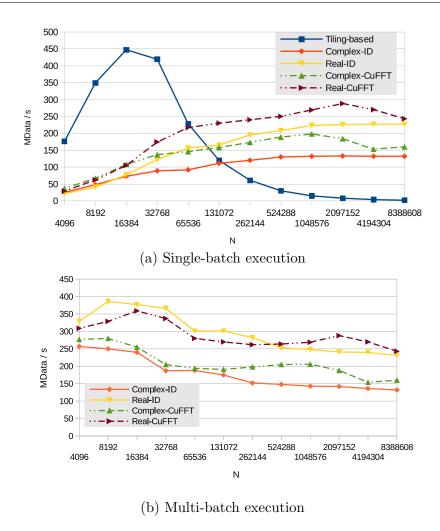

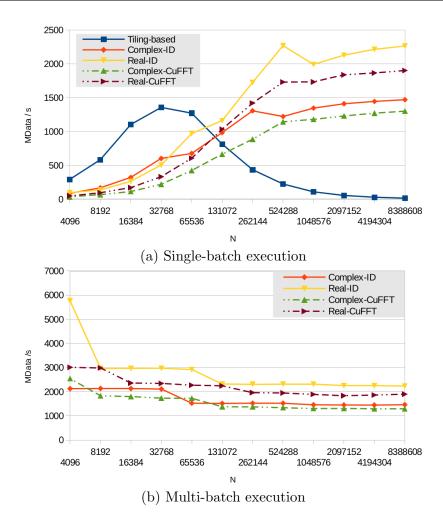

| 5.3. Performance comparison of $MS - ID - TS$ proposal                                                | 49 |

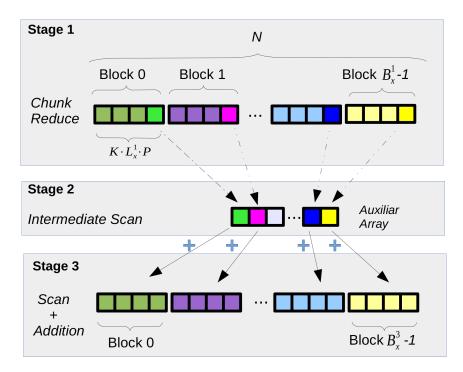

| 5.4. Three kernel execution for the scan primitive when $G=1$ problems.                               | 57 |

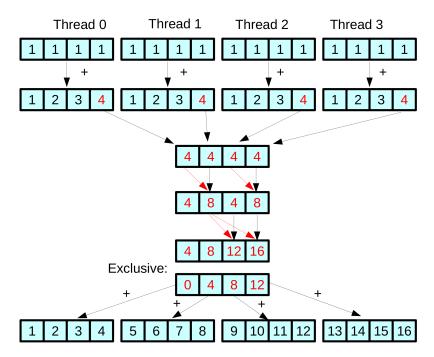

| 5.5. Scan computation in one warp, considering $warpSize=4$ , $P=4$ and $L_x=4$                       | 59 |

| 5.6. Cascade approach computation                                                                     | 59 |

| 5.7. <i>TPR</i> forward reduction                                                                     | 33 |

XLVI List of Figures

| 5.8.  | TPR backward substitution                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 5.9.  | Forward Reduction code for the <i>TPR</i> tridiagonal algorithm using BPLG                                                                    |

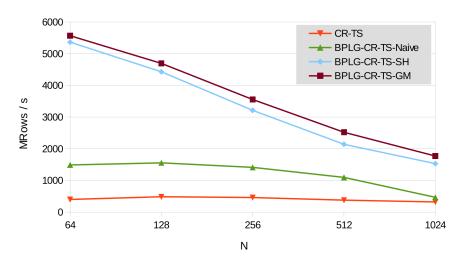

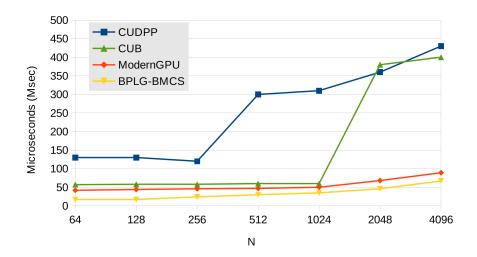

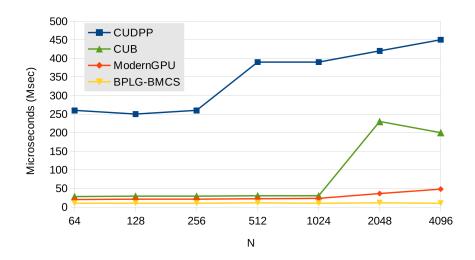

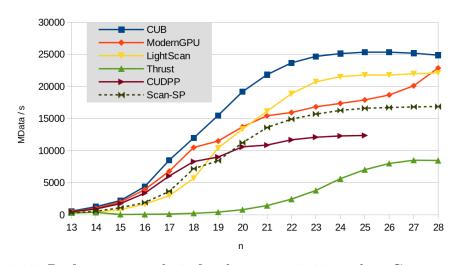

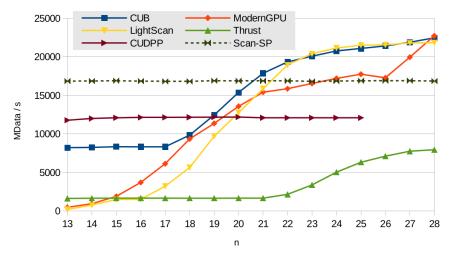

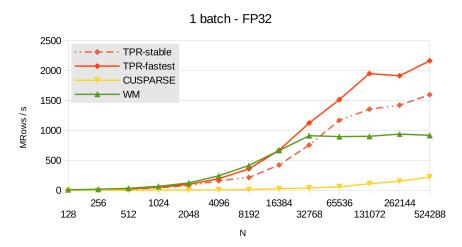

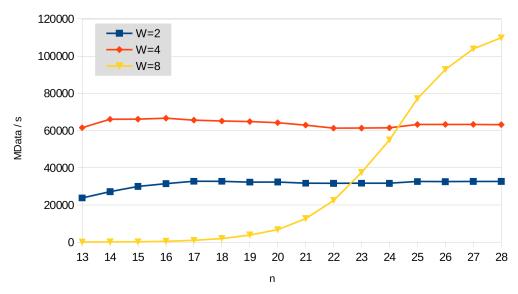

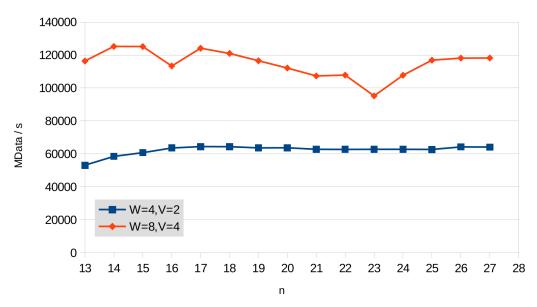

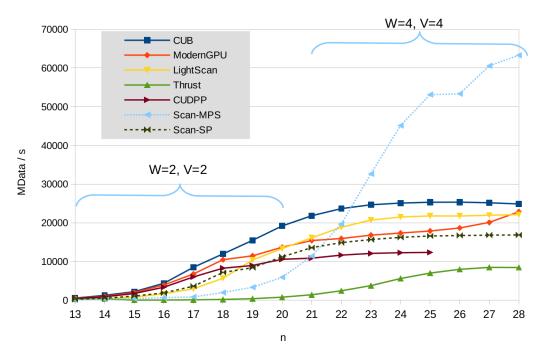

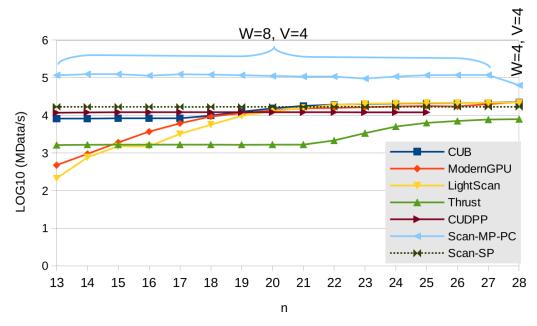

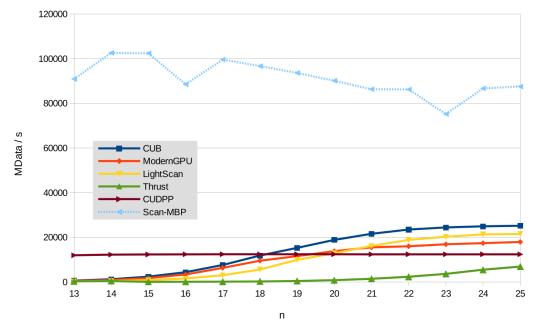

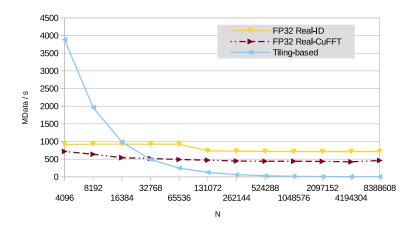

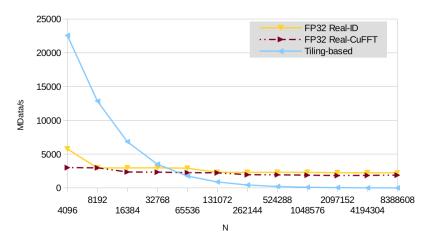

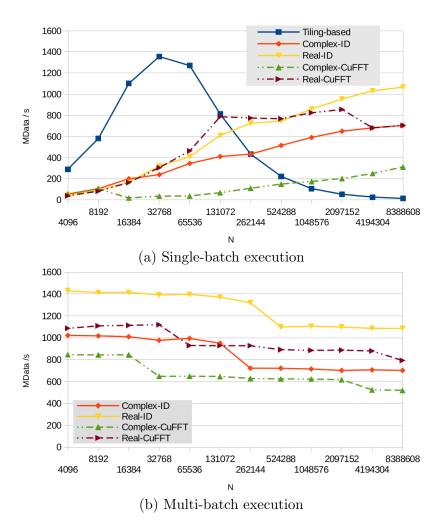

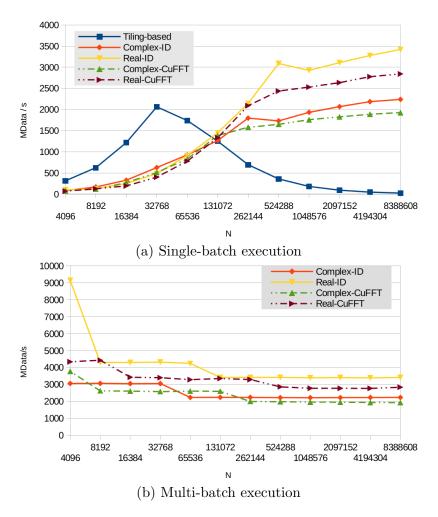

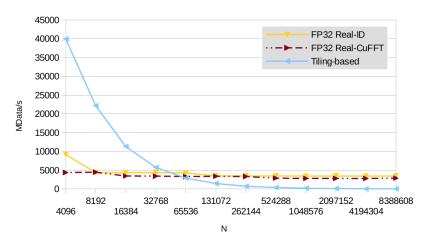

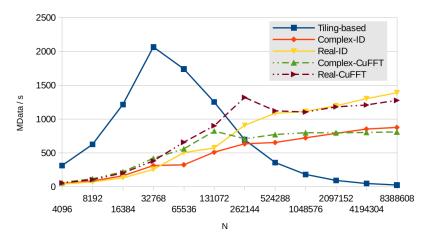

| 5.10. | Performance analysis for the scan primitive when $G=1$ problems 168                                                                           |

| 5.11. | Performance analysis for the scan primitive with $G$ problems 168                                                                             |

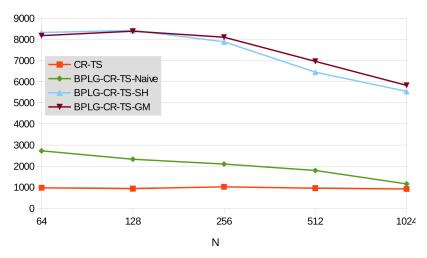

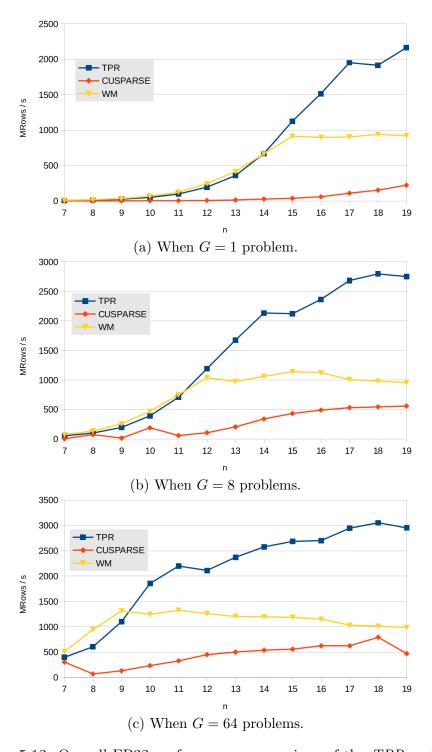

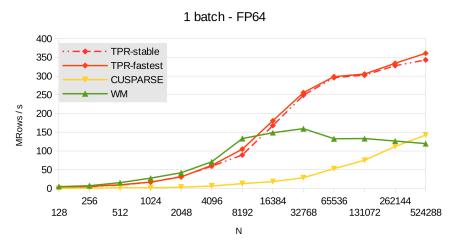

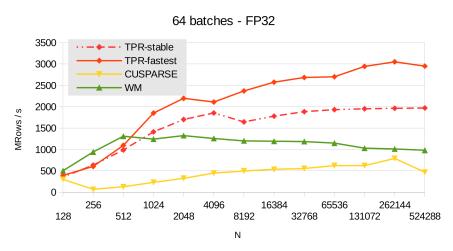

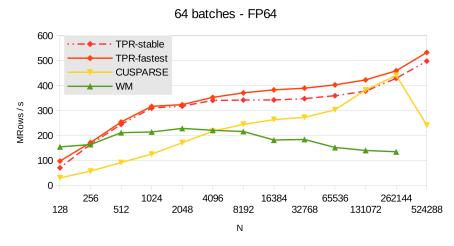

| 5.12. | Overall FP32 performance comparison of the $TPR$ method 170                                                                                   |

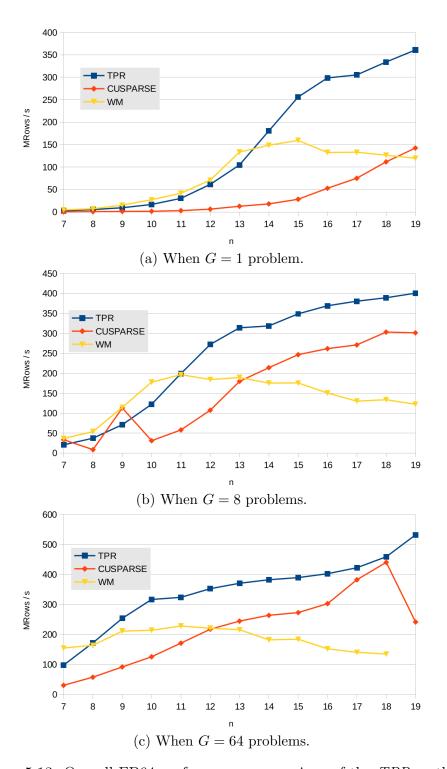

| 5.13. | Overall FP64 performance comparison of the $TPR$ method 172                                                                                   |

| 5.14. | Performance comparison of two different TPR configurations: performance vs numerical stability, executing 1 batch in simple precision 173     |

| 5.15. | Performance comparison of two different TPR configurations: performance vs numerical stability, executing 1 batch in double precision.        |

| 5.16. | Performance comparison of two different TPR configurations: performance vs numerical stability, executing 64 batches in simple precision. 174 |

| 5.17. | Performance comparison of two different TPR configurations: performance vs numerical stability, executing 64 batches in double precision. 174 |

| 6.1.  | Multi-GPU topology within a Multi-Node environment                                                                                            |

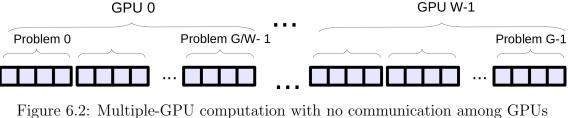

| 6.2.  | Multiple-GPU computation with no communication among GPUs 181                                                                                 |

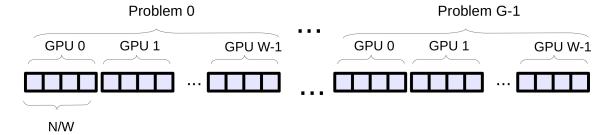

| 6.3.  | Multiple-GPU computation with communication among devices 181                                                                                 |

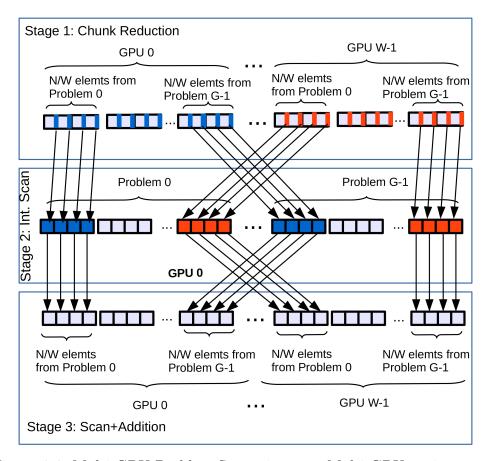

| 6.4.  | Multi-GPU Problem Scattering on a Multi-GPU environment 186                                                                                   |

| 6.5.  | Pseudo-code of Scan-MPS in a Multi-Node environment                                                                                           |

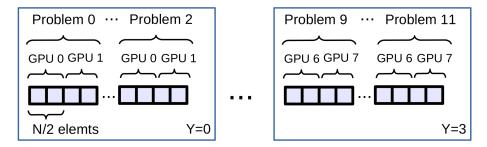

| 6.6.  | 12 problems being solved by 4 different PCI-e networks with 2 GPUs each                                                                       |

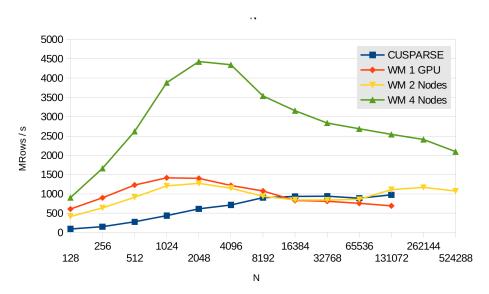

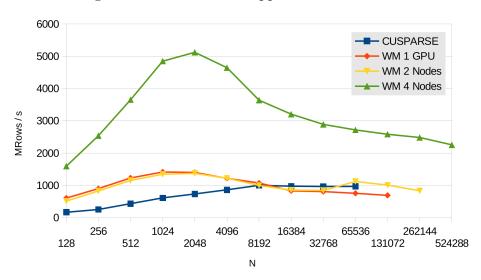

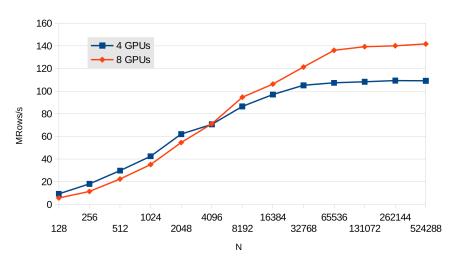

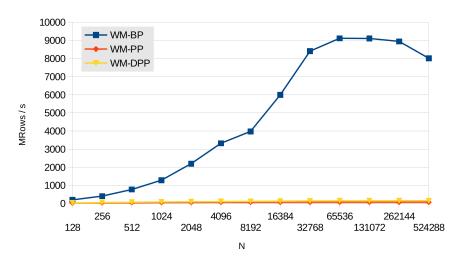

| 6.7.  | Performance analysis for the Multi-GPU Problem Scattering approach (Scan-MPS proposal) where $G = 2^{28}/N$                                   |

List of Figures XLVII

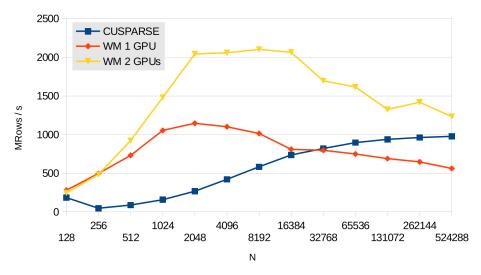

| 6.8.  | Performance analysis for the Multi-GPU Problem with Prioritized Communications approach (Scan-MP-PC proposal) where $G = 2^{28}/N$ . 192            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.9.  | Performance analysis for our best Multi-GPU proposal when $G=1.$ . 192                                                                              |

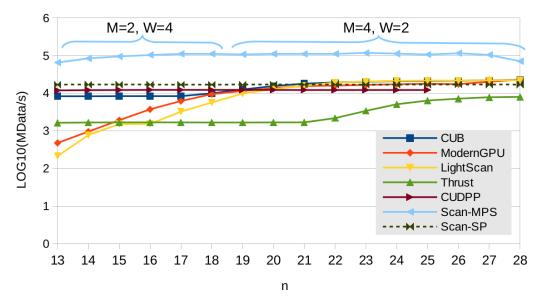

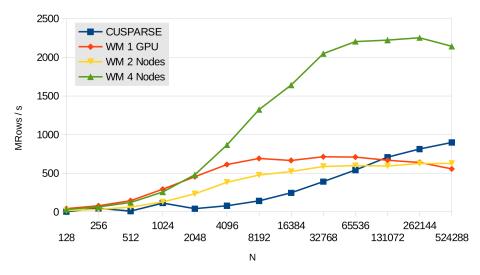

| 6.10. | Performance analysis for our best Multi-GPU proposal when $G=2^{28}/N$ problems                                                                     |

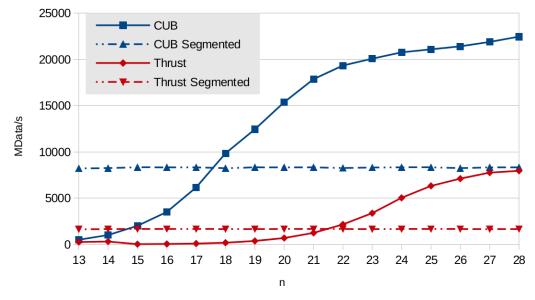

| 6.11. | Comparison of $CUB$ and $Thrust$ libraries under a segmented execution when $G=2^{28}/N$ problems                                                   |

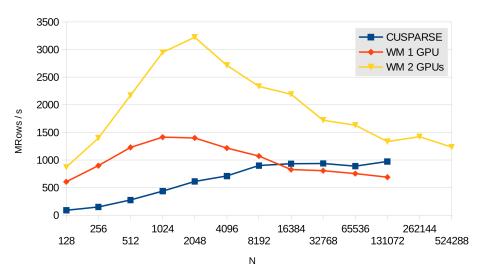

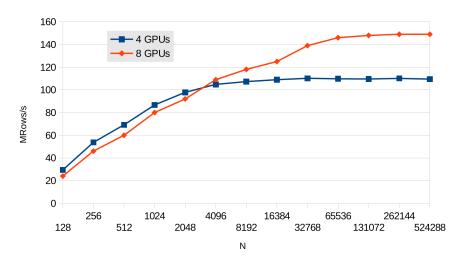

| 6.12. | Performance analysis for the Multi-GPU Batch Parallelism approach (Scan-MBS proposal) where $G=2^{26}/N$                                            |

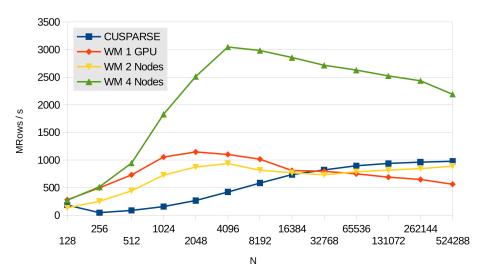

| 6.13. | Performance analysis for our best Multi-Node proposal for $G=2^{28}/N$ problems                                                                     |

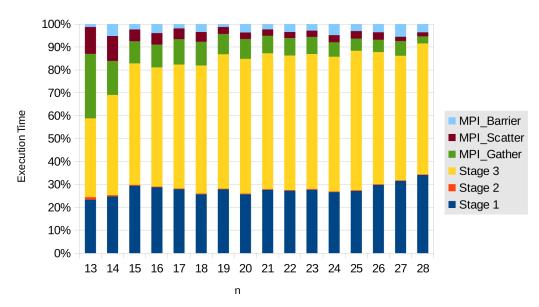

| 6.14. | Breakdown of times spent on M=2 and W=4 for $G=2^{28}/N$ problems.198                                                                               |

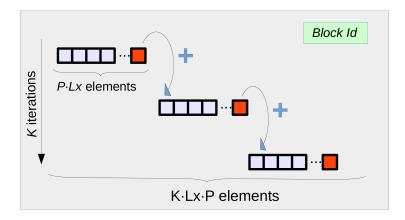

| 6.15. | Multi-GPU approach with $W$ GPUs for solving $G$ problems of $N$ elements: Each GPU solves $G/W$ entire problems of $N$ elements 201                |